# Continue - Application of Combinational Logic Circuit / DECODER- ENCODER & Bit Converters

First Class

- **Decoder** Is a digital circuit that detects the presence of a specified combination of bits (code) on its input and indicates the presence of that code by a specified output level.

- **Decoding** Is the conversion of an *n*-bit input code to an *m*-bit output code with  $n \le m \le 2^n$  such that each valid code word produces a unique output code

- Circuits that perform decoding are called *decoders*

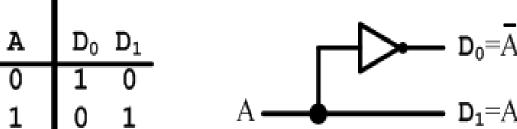

- This a 1-to-2 Line decoder exactly one of the output lines will be active.

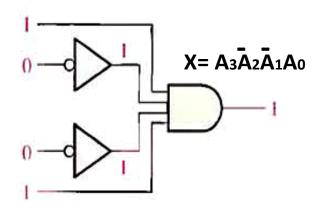

Example: Determine the logic required to decode the binary

Number 1001 by producing a High level on the output

**Solution**: You must be sure that all of the inputs to the AND gate are HIGH when the binary number 1001 occurs,

$$X = A_3 \overline{A}_2 \overline{A}_1 A_0$$

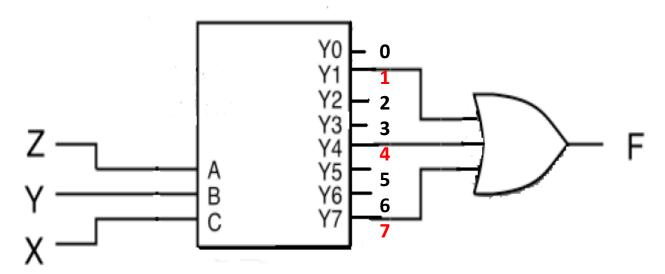

• Example: Realize F  $(X,Y,Z) = \Sigma (1, 4, 7)$  with a decoder Solution: 1, 4, 7 means the three outputs obtained from eight output.

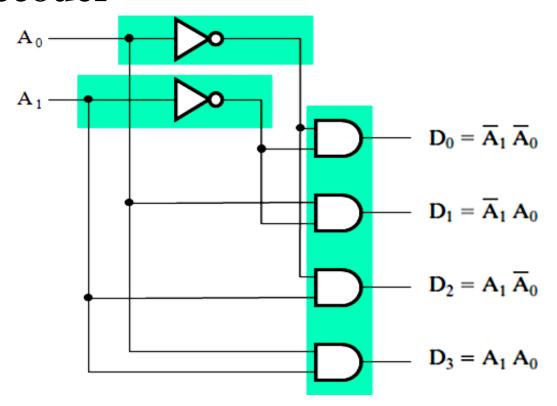

### • A 2-to-4 line decoder

| <b>A</b> <sub>1</sub> | $\mathbf{A}_0$ | Do | $D_1$ | $D_2$ | D <sub>3</sub> |

|-----------------------|----------------|----|-------|-------|----------------|

| 0                     | 0              | 1  | 0     | 0     | 0              |

| 0                     | 1              | 0  | 1     | 0     | 0              |

| 1                     | 0              | 0  | 0     | 1     | 0              |

| 1                     | 1              | 0  | 0     | 0     | 1              |

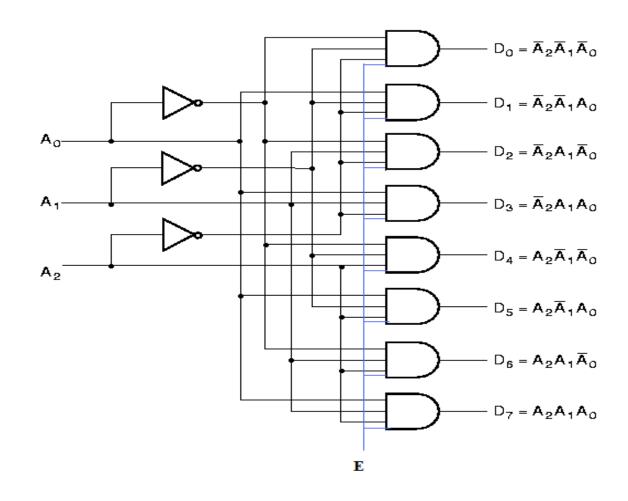

- 2-to-4,

- 3-to-8,

- ...

- n-to-2<sup>n</sup>

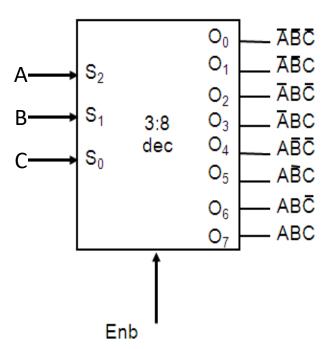

| Enb | A | В | С | O0 | 01 | O2 | O3 | O4 | O5 | O6 | <b>O</b> 7 |

|-----|---|---|---|----|----|----|----|----|----|----|------------|

| 0   | Х | Х | Х | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0          |

| 1   | 0 | 0 | 0 | 1  |    |    |    |    |    |    |            |

| 1   | 0 | 0 | 1 |    | 1  |    |    |    |    |    |            |

| 1   | 0 | 1 | 0 |    |    | 1  |    |    |    |    |            |

| 1   | 0 | 1 | 1 |    |    |    | 1  |    |    |    |            |

| 1   | 1 | 0 | 0 |    |    |    |    | 1  |    |    |            |

| 1   | 1 | 0 | 1 |    |    |    |    |    | 1  |    |            |

| 1   | 1 | 1 | 0 |    |    |    |    |    |    | 1  |            |

| 1   | 1 | 1 | 1 |    |    |    |    |    |    |    | 1          |

### 3-to-8 Decoder with Enable

# Application of Decoder

• Example: Realize the 1 bit-binary adder circuit using decoder.

**Solution**: The truth table is as shown, so the output function should be:

Truth Table for 1-bit Binary Adder

| $S(X, Y, Z) = \sum_{i=1}^{n} m(1, Z, 4, I)$ | <i>'</i> ) |

|---------------------------------------------|------------|

| $C(X, Y, Z) = \sum m(3, 5, 6, 7)$           | 7)         |

| X                | Υ                     | Z                     | С                     | s                |                                                       |

|------------------|-----------------------|-----------------------|-----------------------|------------------|-------------------------------------------------------|

| 0<br>0<br>0<br>0 | 0<br>0<br>1<br>1<br>0 | 0<br>1<br>0<br>1<br>0 | 0<br>0<br>0<br>1<br>0 | 0<br>1<br>1<br>0 | 3-to-8-line<br>Decoder  20 20 5                       |

| 1<br>1<br>1      | 0<br>1<br>1           | 1<br>0<br>1           | 1<br>1<br>1           | 0<br>0<br>1      | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$ |

# Application of Decoder

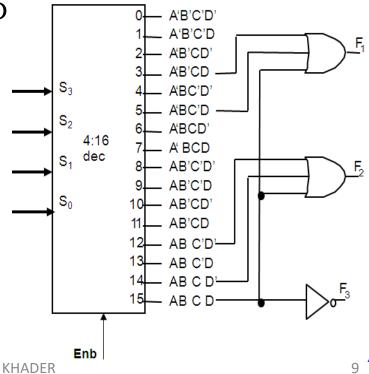

#### Implementing General Logic

Any combinational circuit can be constructed using decoders and OR gates!

**Example**: design a circuit that can realize the output below:

Solution:

Note: X' means  $\overline{X}$

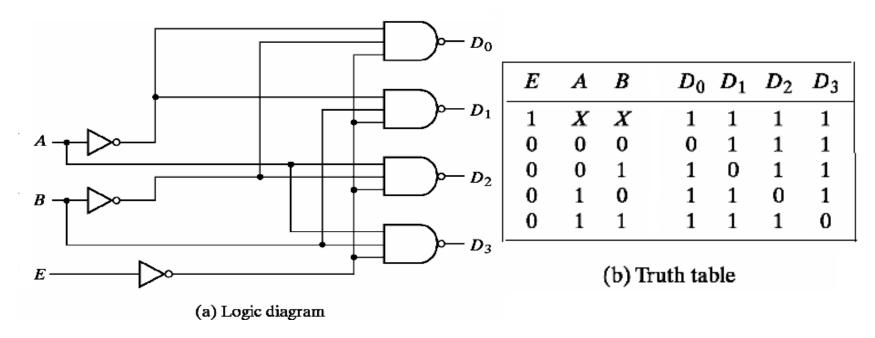

### **Active Low Decoder**

- If an active-low output is required for each decoded number, the entire decoder can be implemented with NAND gates and inverters.

- **Example**: 2-to-4 Decoder is enabled when E=0 and an output is active if it is 0

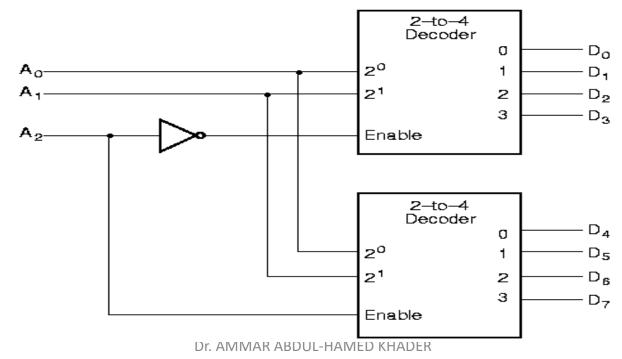

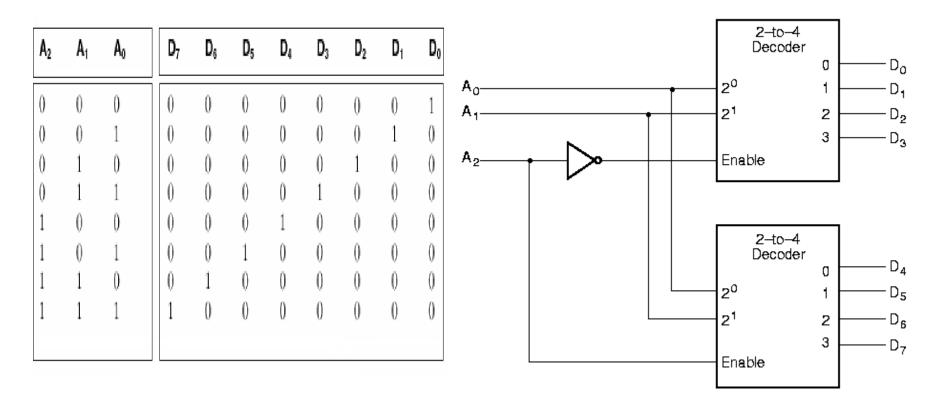

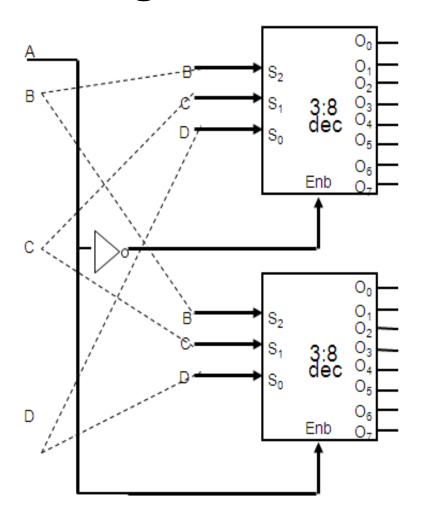

# **Decoder Expansion**

#### Decoder expansion

- Combine two or more small decoders with enable inputs to form a larger decoder. 3-to-8-line decoder constructed from two 2-to-4-line decoders

- The MSB is connected to the enable inputs

- if  $A_2$ = 0, upper is enabled; if  $A_2$ =1, lower is enabled.

# Combining Two 2-4 Decoders to Form One 3-8 Decoder Using Enable Switch

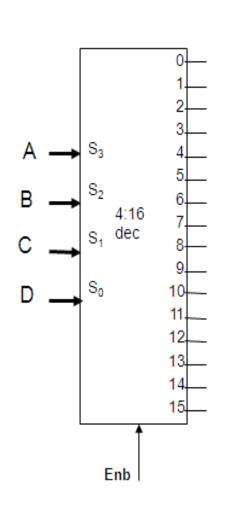

# Combining Two 3-8 Decoders to Form One 4-16 Decoder Using Enable Switch

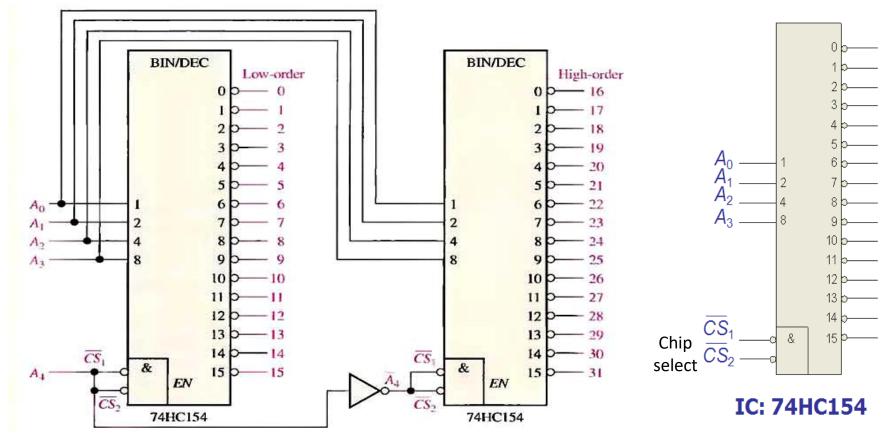

# 74HC154 Integrated Circuit

- **Example**: A certain application requires that a 5-bit number be decoded. Use a 74HC154 IC decoders to implement the logic.

- Solution: Since this IC handle only 4-bits, two decoder must be used.

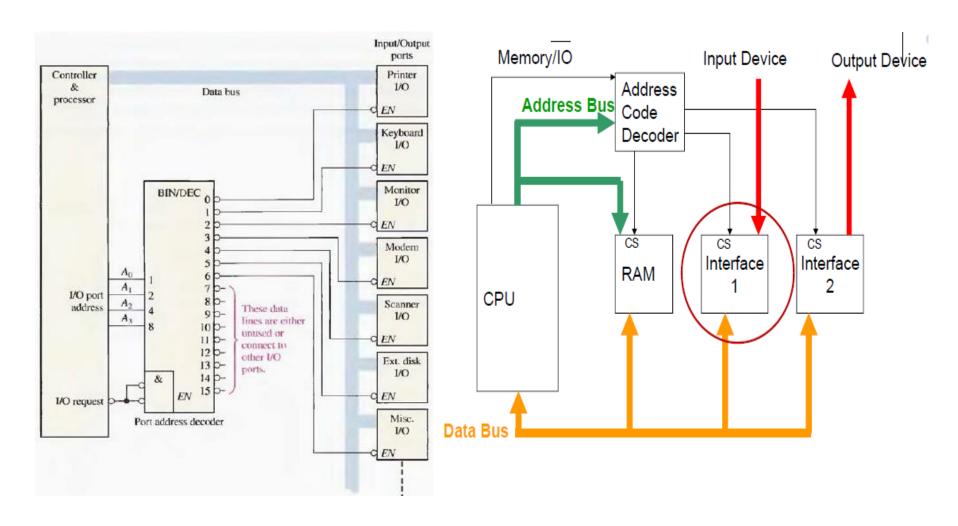

### Application of Decoder in Computer

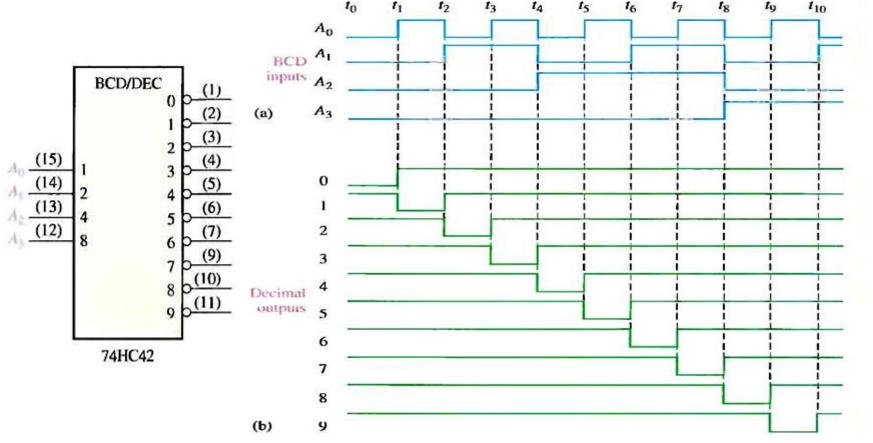

### The BCD to Decimal Decoder

• It convert each BCD (8421 code) into one-to-ten possible decimal digit indications. It is called 4-to-10 line decoder or a

1-to-10 decoder.

| DECIMAL |     | BCD C          | DECODING |    |                                                            |

|---------|-----|----------------|----------|----|------------------------------------------------------------|

| DIGIT   | A 3 | A <sub>2</sub> | $A_1$    | Ao | FUNCTION                                                   |

| 0       | 0   | 0              | 0        | 0  | $\overline{A}_3\overline{A}_2\overline{A}_1\overline{A}_0$ |

| 1       | 0   | 0              | 0        | 1  | $\overline{A}_3\overline{A}_2\overline{A}_1A_0$            |

| 2       | 0   | 0              | 1        | 0  | $\overline{A}_3\overline{A}_2A_1\overline{A}_0$            |

| 3       | 0   | 0              | 1        | 1  | $\overline{A}_3\overline{A}_2A_1A_0$                       |

| 4       | 0   | 1              | 0        | 0  | $\overline{A}_3 A_2 \overline{A}_1 \overline{A}_0$         |

| 5       | 0   | 1              | 0        | 1  | $\overline{A}_3 A_2 \overline{A}_1 A_0$                    |

| 6       | 0   | 1              | 1        | 0  | $\overline{A}_3 A_2 A_1 \overline{A}_0$                    |

| 7       | 0   | 1              | 1        | 1  | $\overline{A}_3 A_2 A_1 A_0$                               |

| 8       | 1   | 0              | 0        | 0  | $A_3\overline{A}_2\overline{A}_1\overline{A}_0$            |

| 9       | 1   | 0              | 0        | 1  | $A_3\overline{A_2}\overline{A_1}A_0$                       |

### The BCD to Decimal Decoder

• Example: the 74HC42 is an IC BCD-to-decimal decoder. If the input waveforms as in Fig. are applied to the IC inputs, show the output waveforms.

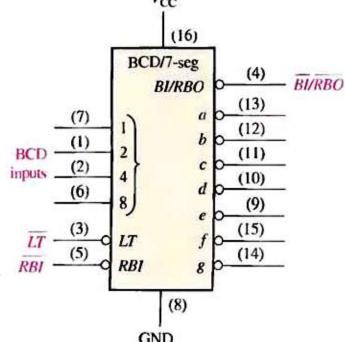

# The BCD to 7-Segment Decoder

• This decoder accept the BCD code on its input and provides outputs to drive 7-segment display devices to produce a decimal readout.  $v_{cc}$

• As an example, the 74LS47. LT (Lamp Test), RBI (Ripple Blanking Input), BI/RBO (Blanking Input/ Ripple Blanking Output). All output are nonactive (HIGH) if (0000) is on inputs and if RBI is low. This causes the display to be blank and produces a LOW RBO.

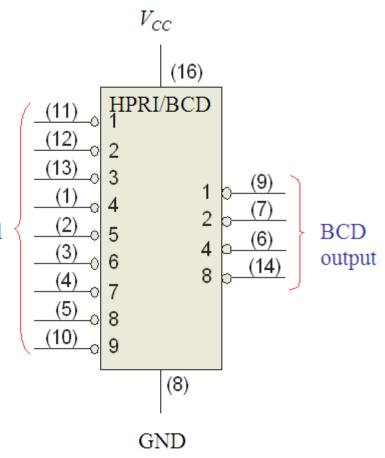

### **Encoder**

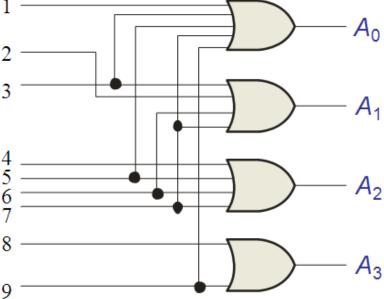

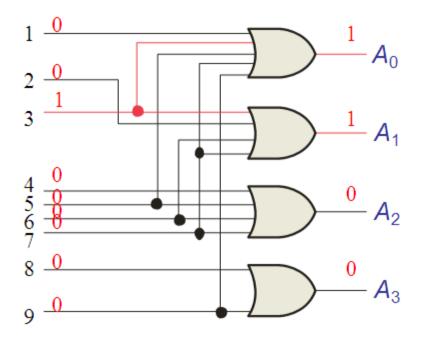

• An encoder is a combinational logic cct. that essentially performs a reverse decoder function. It is accepts an active logic level on one of its inputs representing a digit, such as a decimal or octal digits, and converts it to a coded output, such as BCD or binary.

• IC: 74HC147 16-to-4 encoder (decimal-to-BCD)

• IC: 74F148 8-to-3 encoder

### **Encoder**

Show how the decimal-to-BCD encoder converts the decimal number 3 into a BCD 0011.

### **Encoder**

The 74HC147 is an example of an IC encoder (Decimal-to-BCD). It has ten active-LOW inputs and converts the active input to an active-LOW BCD output.

Decimal input

74HC147

### **Code Converters**

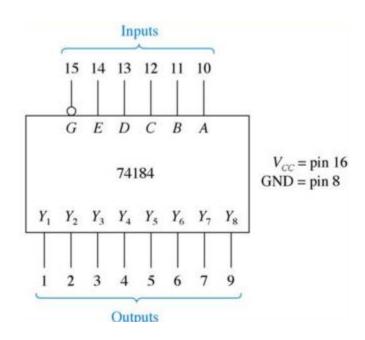

- BCD-to-Binary Conversion

- IC: 74184

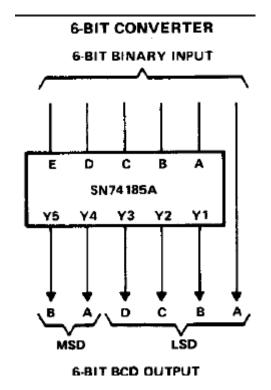

- Binary-to-BCD Conversion

- IC: 74185

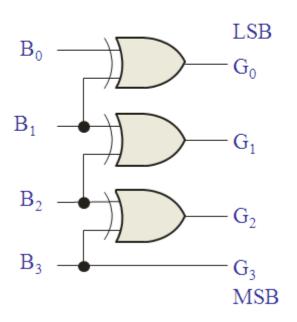

### **Code Converters**

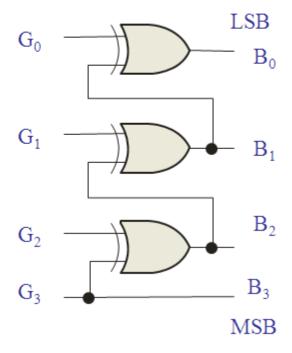

BIN-to-Gray

Gray-to-BIN