Sequential logic circuits

First Class

1

Dr. AMMAR ABDUL-HAMED KHADER

INTRODUCTION

• Combinational Logic:

– Output depends only on current input

– Has no memory

– The design depends mainly on Logic Gates

• No way of remembering or storing information after inputs

have been removed.

• To handle this, we need sequential logic capable of storing

intermediate (and final) results.

• Sequential Logic:

– Output depends not only on current input but also on past input

values, e.g., design a counter

– Need some type of memory to remember the past input values

– The design depends mainly on Flip-Flop Circuit

2

Dr. AMMAR ABDUL-HAMED KHADER

Sequential Logic Circuits

3

Dr. AMMAR ABDUL-HAMED KHADER

Sequential circuits can be Asynchronous or synchronous.

Asynchronous

sequential circuits change their states and

output values whenever a change in input values

occurs.

Synchronous

sequential circuits change their states and

output values at fixed points of time, i.e. clock signals.

Sequential Logic Circuits

4

Dr. AMMAR ABDUL-HAMED KHADER

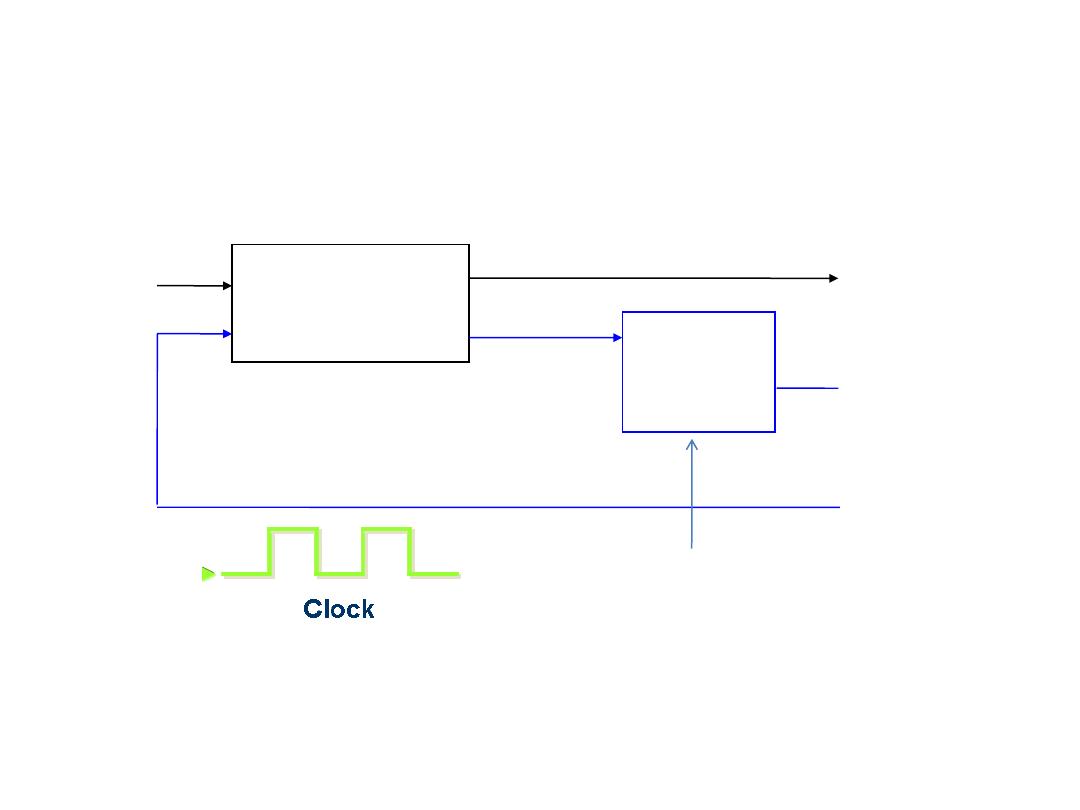

Combinational

circuit

Storage

Element

Flip Flops

Outputs

Inputs

Next

state

Present

state

Timing signal

(clock)

5

Dr. AMMAR ABDUL-HAMED KHADER

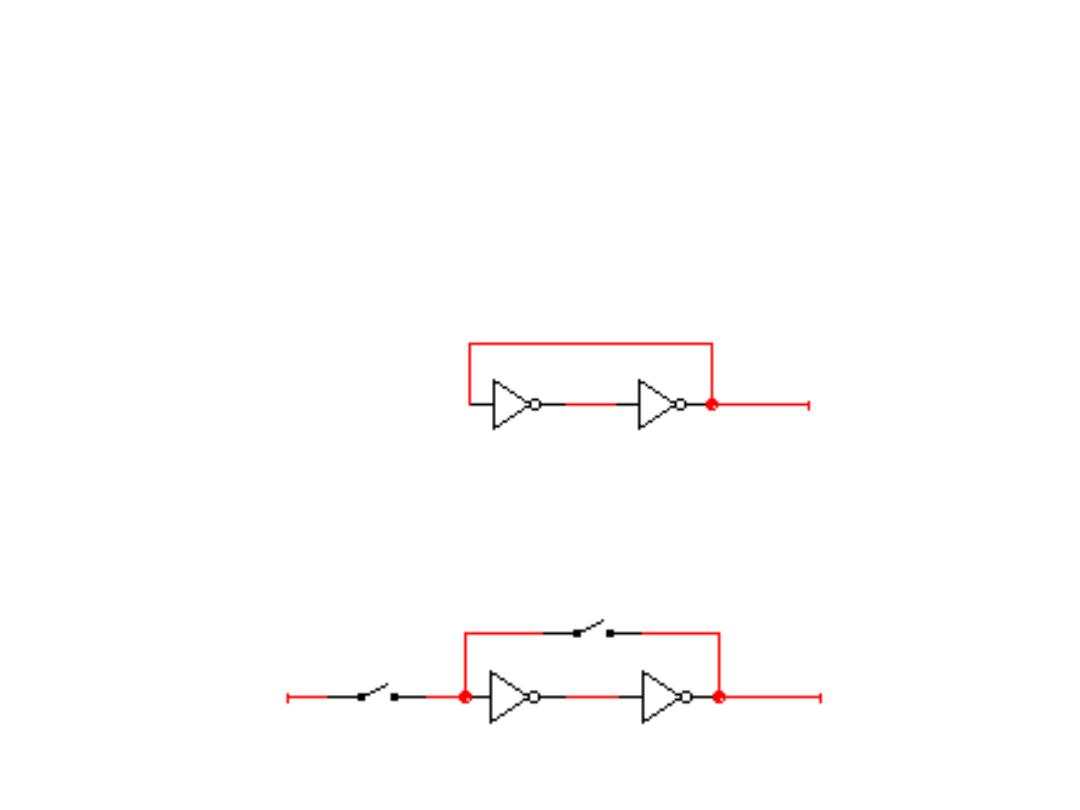

Storage Element

"0"

"1"

"stored value"

"remember"

"load"

"data"

"stored value"

• Two inverters form a static memory cell

– will hold value as long as it has power applied

• How to get a new value into the memory cell?

– selectively break feedback path

– load new value into cell

Sequential Logic Circuits

•

Multivibrators Logic Devices:

Bistable device: have two stable states, called SET and

RESET.

Monostable device: commonly known as the One-shot, it has

only one stable state.

Astable device: has no stable state and is used primarily as an

oscillator, which is a self-sustained waveform generator.

6

Dr. AMMAR ABDUL-HAMED KHADER

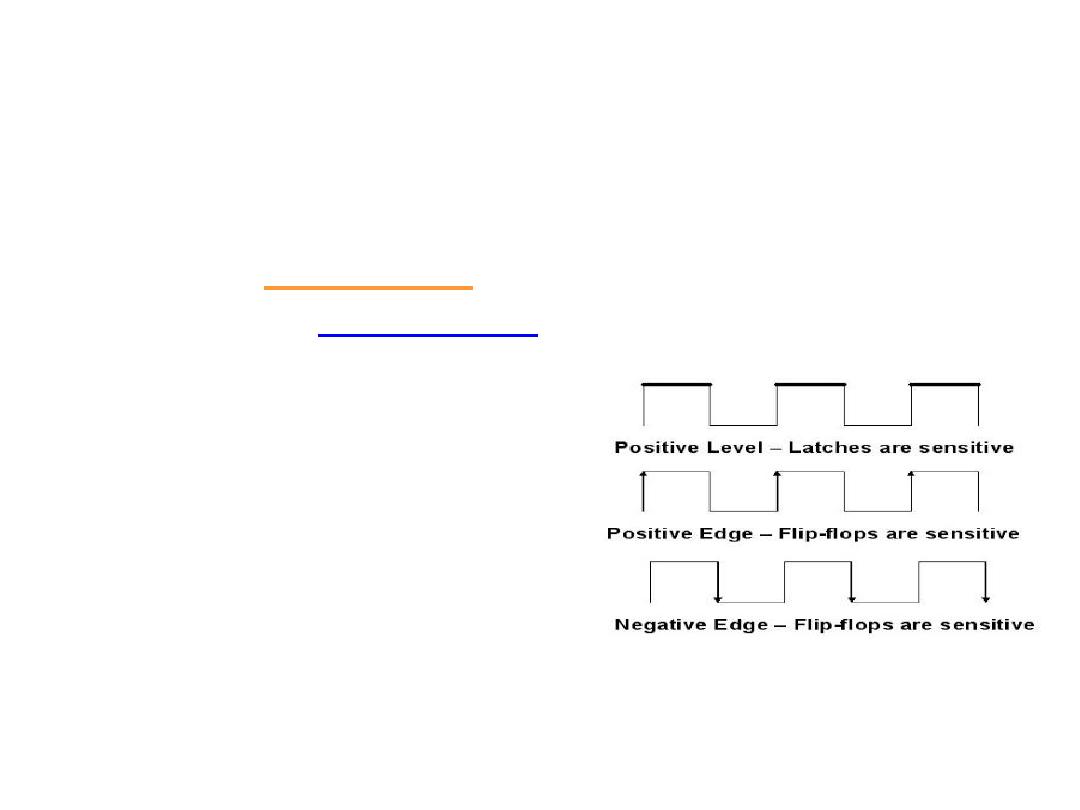

Storage Cells

• The two most popular varieties of storage cells used to build

sequential circuits are: latches and flip-flops.

– Latch:

level sensitive

storage element

– Flip-Flop:

edge triggered

storage element

• Common examples of latches:

S-R latch, \S-\R latch, D latch

(= gated D latch)

Common examples of flip-flops:

D-FF, D-FF with enable,

Scan-FF, JK-FF, T-FF

Dr. AMMAR ABDUL-HAMED KHADER

7

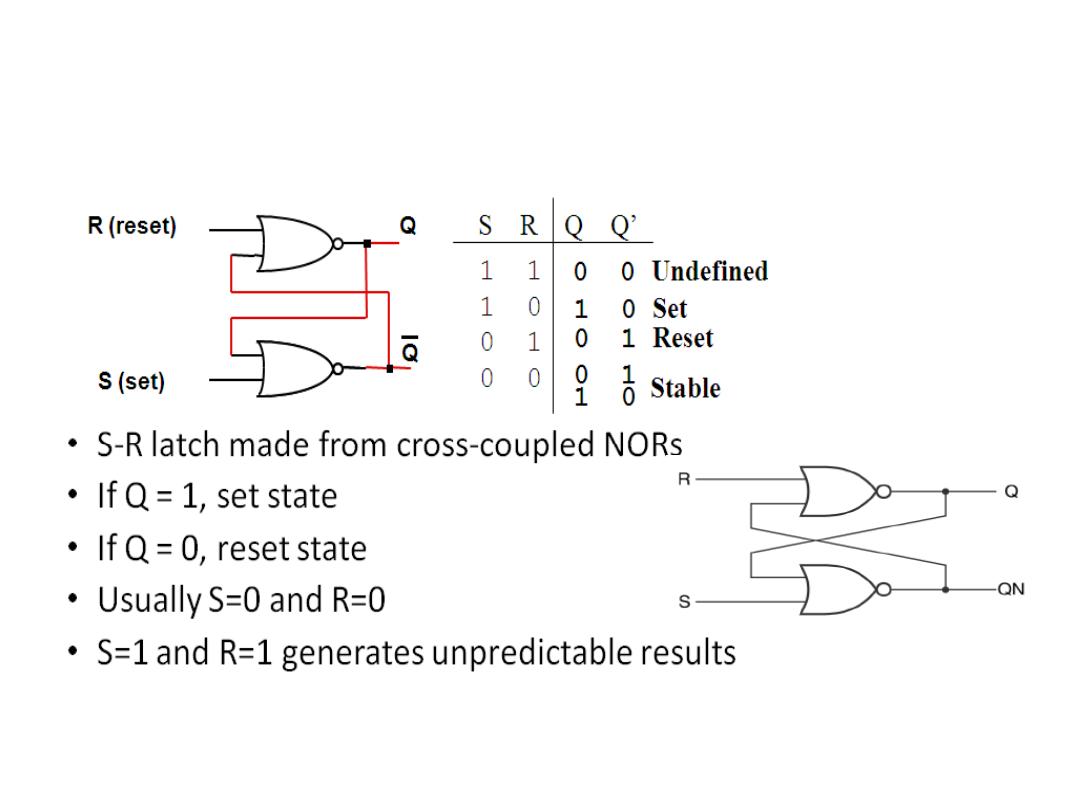

S-R Latch with NORs

Dr. AMMAR ABDUL-HAMED KHADER

8

- No change

- Not allowed

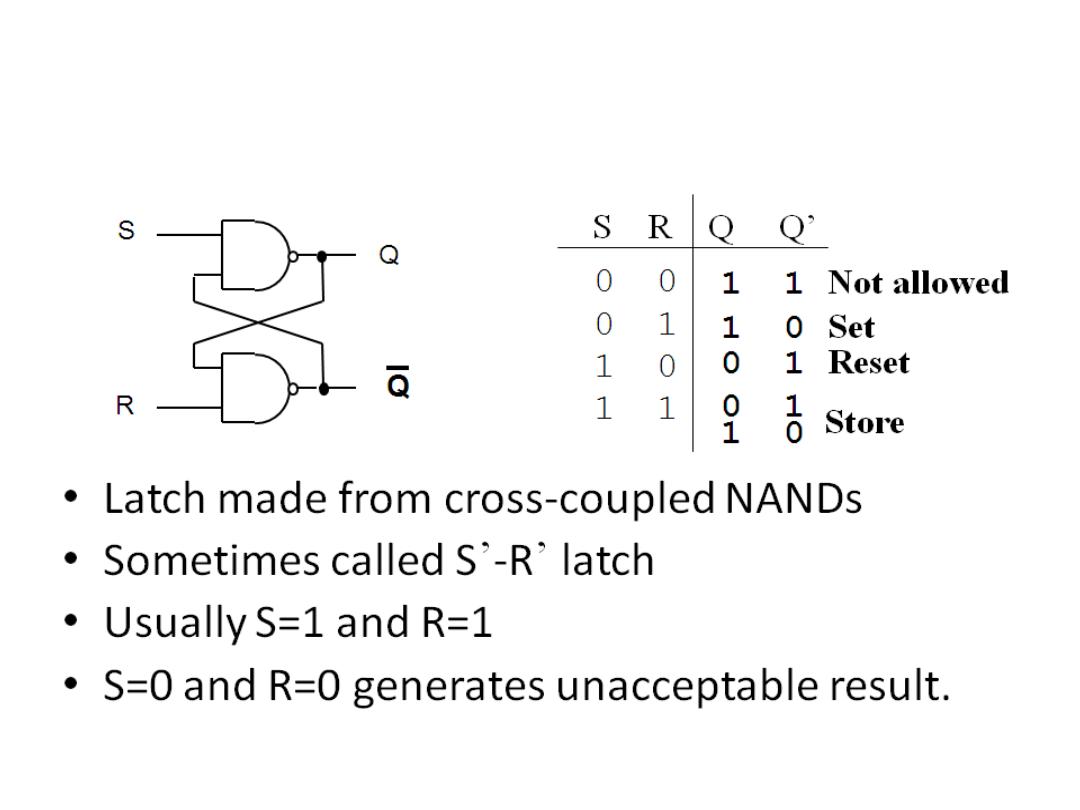

S-R Latch with NANDs

Dr. AMMAR ABDUL-HAMED KHADER

9

- No change

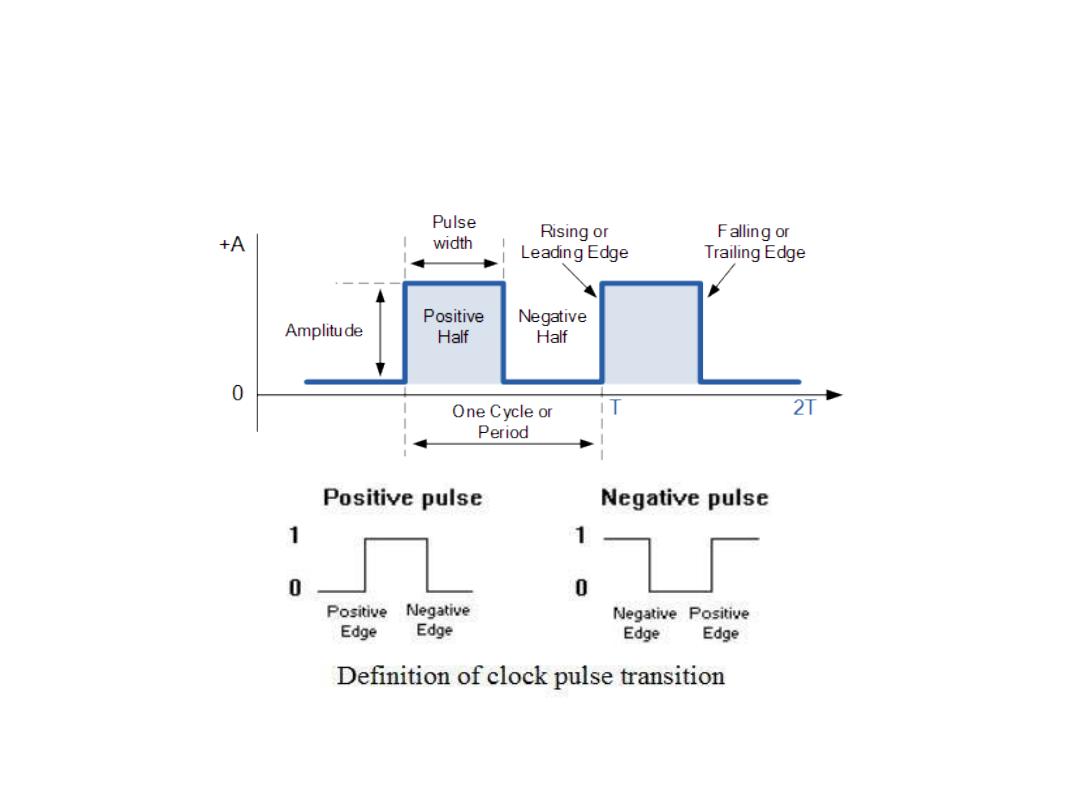

Clock Pulse Definition

Dr. AMMAR ABDUL-HAMED KHADER

10

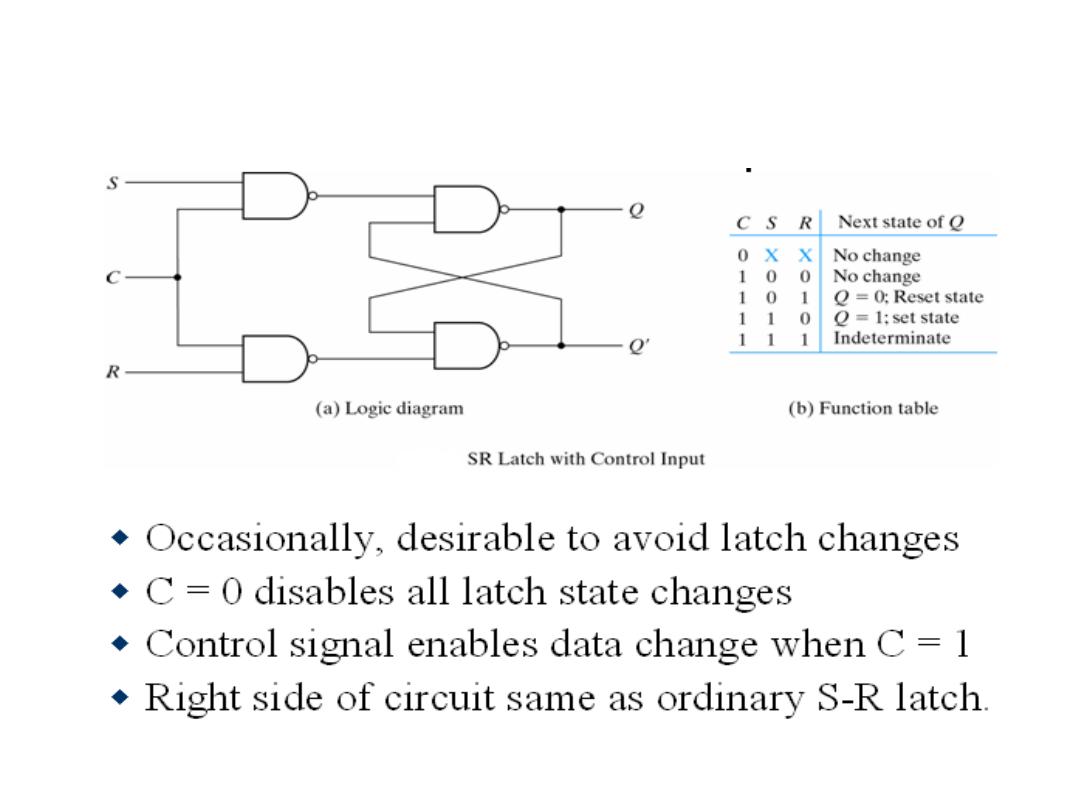

S-R Latch with Control Input

Dr. AMMAR ABDUL-HAMED KHADER

11

- Not allowed

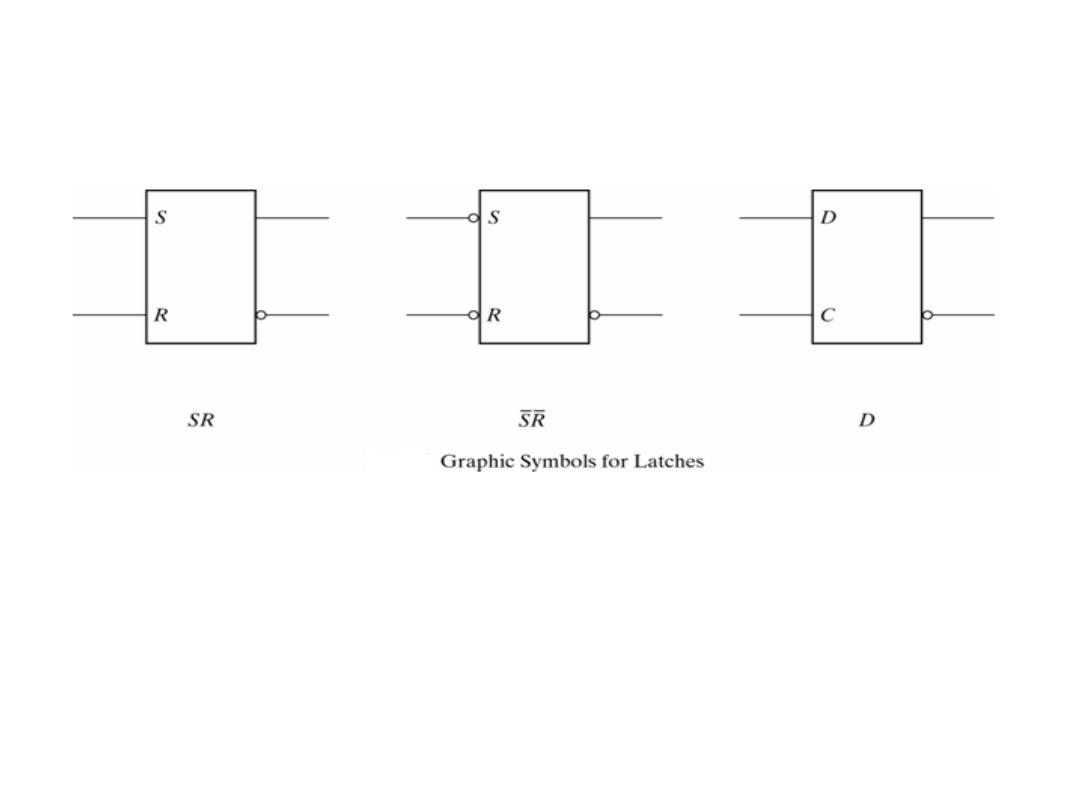

Symbols for Latches

Dr. AMMAR ABDUL-HAMED KHADER

12

• SR latch is based on NOR gates

• S’R’ latch based on NAND gates

• D latch can be based on either.

• D latch sometimes called transparent latch

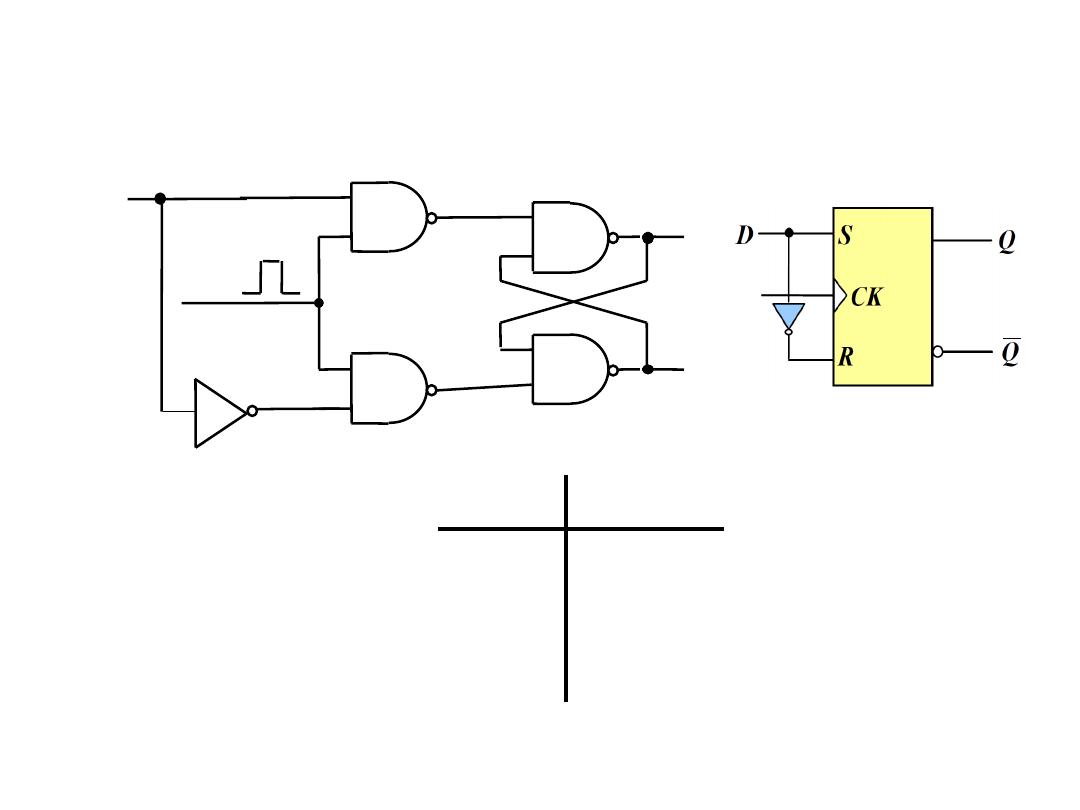

D Latch

Dr. AMMAR ABDUL-HAMED KHADER

13

Q

Q

’

S

R

Y

D

C

0 1 0 1

1 1 1 0

X 0 Q

0

Q

0

’

D

C

Q Q’

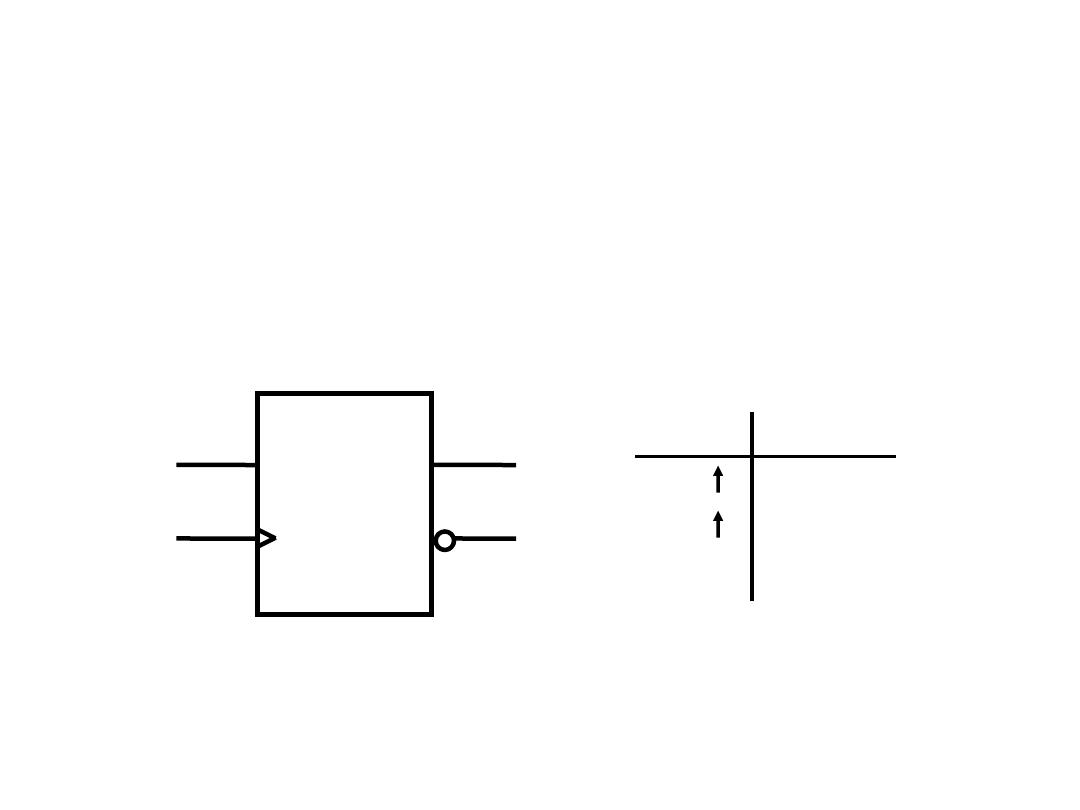

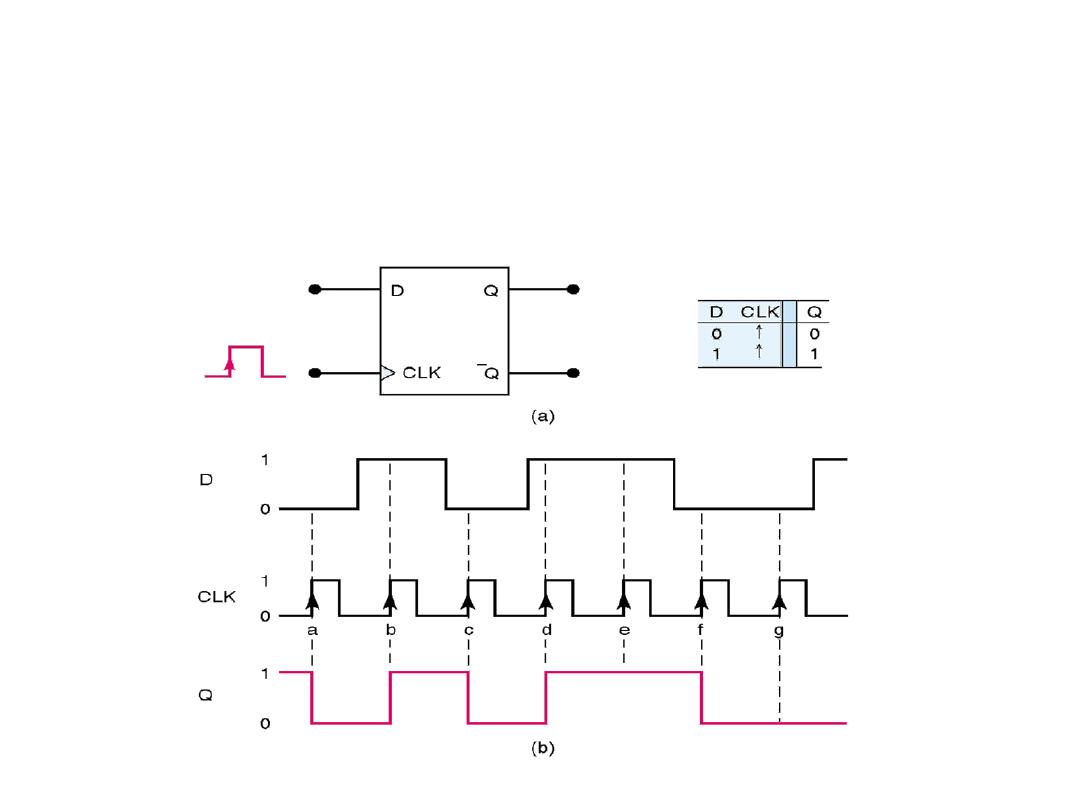

D Flip-Flop

• Stores a value on the positive edge of

C

• Input changes at other times have no effect on output

Dr. AMMAR ABDUL-HAMED KHADER

14

CK

0 0 1

1 1 0

X 0 Q

0

Q

0

’

D

C

Q Q’

Positive edge triggered

D gets latched to Q on the rising edge of the clock.

D

D Flip-Flop

Dr. AMMAR ABDUL-HAMED KHADER

15

Q

n+1

= D

n

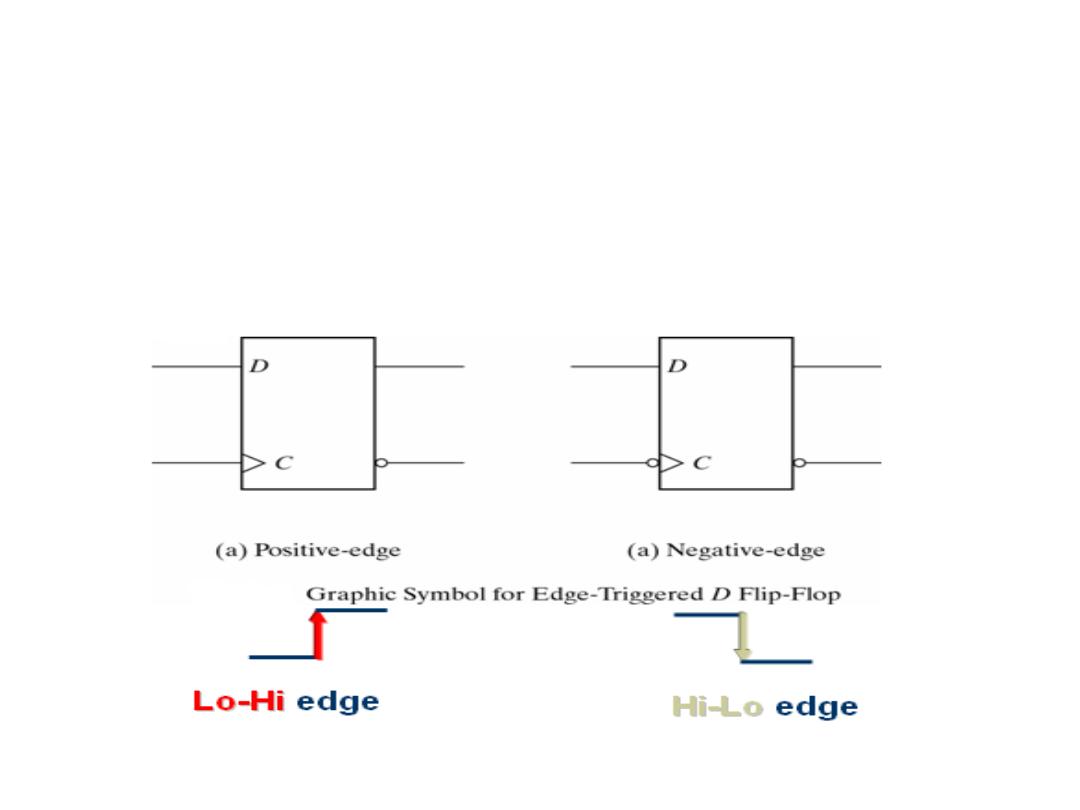

D Flip-Flop

Positive and Negative Edge

• D flops can be triggered on positive or negative edge. Bubble

before

Clock (C)

input indicates negative edge trigger

Dr. AMMAR ABDUL-HAMED KHADER

16

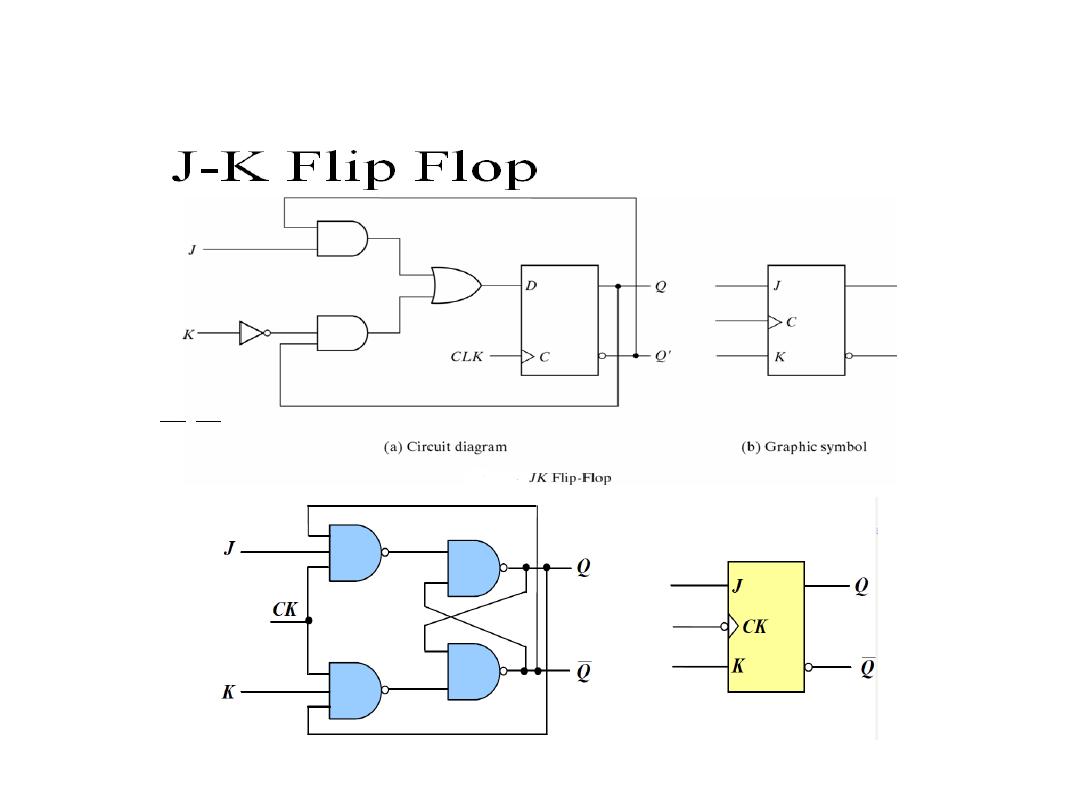

Other Types of Flip-Flops

Dr. AMMAR ABDUL-HAMED KHADER

17

D=J Q+K Q

Clocked

Dr. AMMAR ABDUL-HAMED KHADER

18

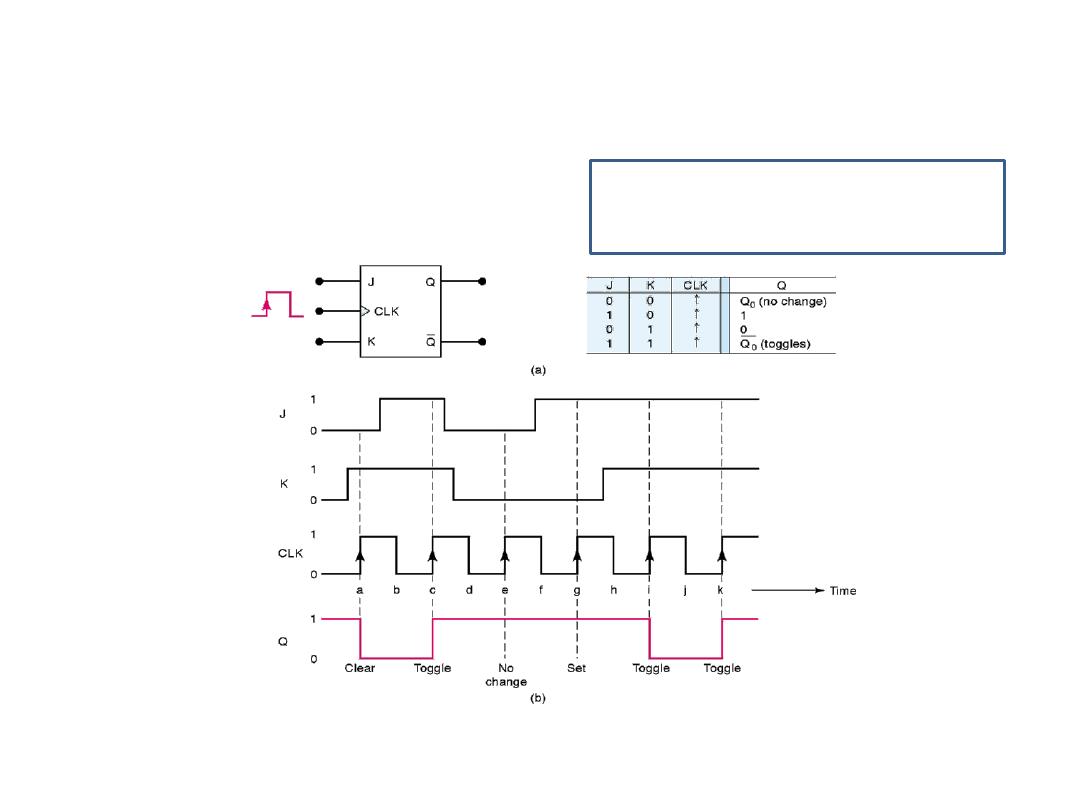

•

Two data inputs, J and K

•

J -> set, K -> reset, if J=K=1 then toggle

output

Characteristic Table

Or Transition Table

J K differs from RS, because there is

NO not allowed state (11)

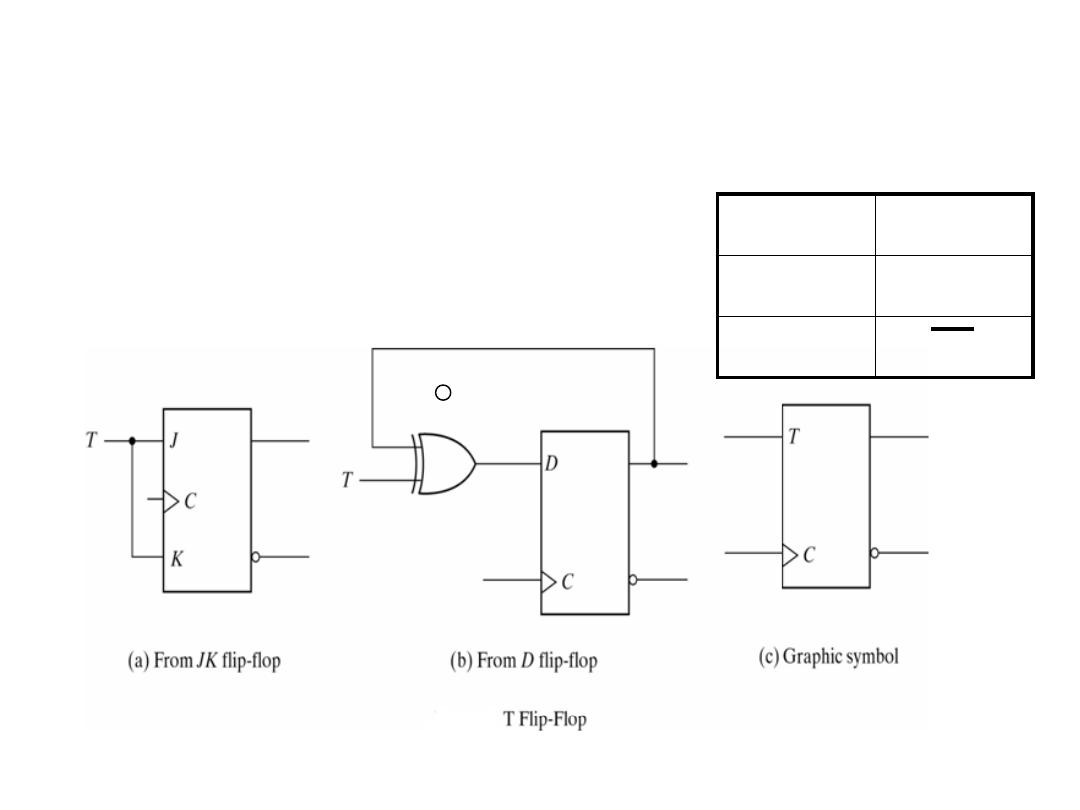

T Flip-Flop

(

Toggle)

Dr. AMMAR ABDUL-HAMED KHADER

19

Q(t+1)

T

Q(t)

0

Q(t)

1

D=T + Q

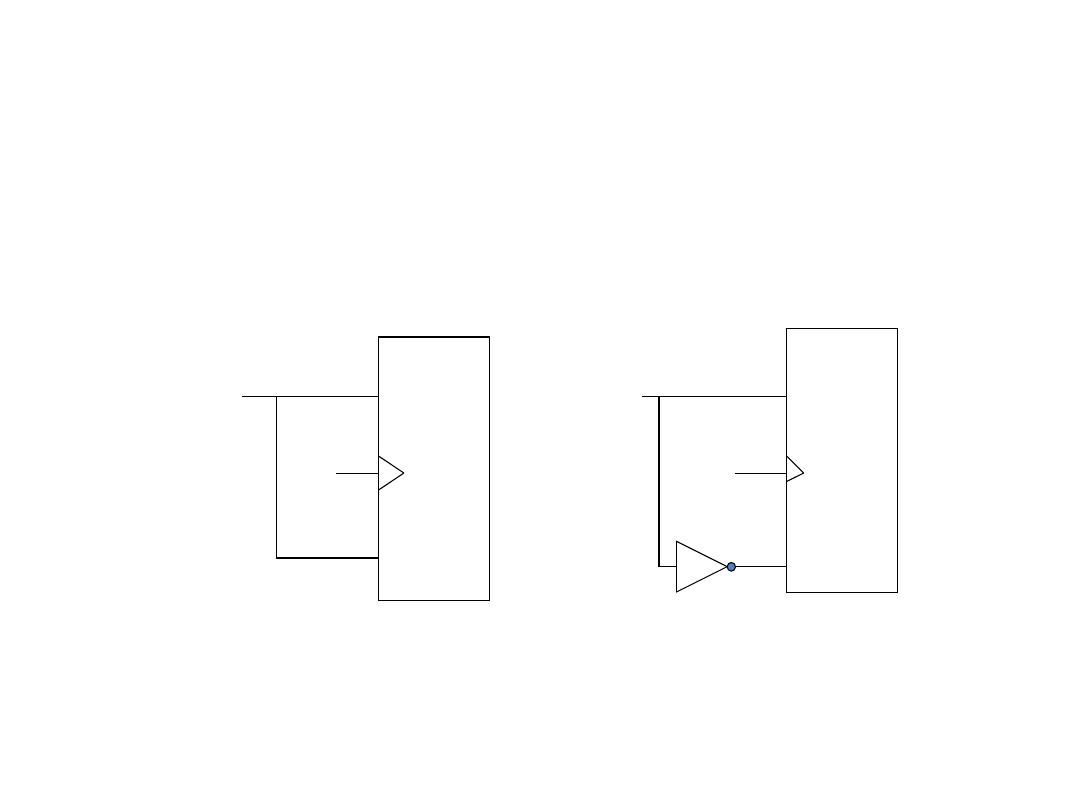

JK Converted to Other FFs

Dr. AMMAR ABDUL-HAMED KHADER

20

J

J

T

K

K

D

C

C

D from JK

T from JK

Summary

Dr. AMMAR ABDUL-HAMED KHADER

21

• Latches are based on combinational gates (e.g. NAND, NOR)

• Latches store data even after data input has been removed

• S-R latches operate like cross-coupled inverters with control inputs

(S = set, R = reset)

• With additional gates, an S-R latch can be converted to a D latch (D

stands for data)

• D latch is simple to understand conceptually

– When C = 1, data input D is stored in latch at the output as Q.

– When C = 0, data input D is ignored and previous latch value is

at the output Q.

Summary

Latch

• – Clock input is level sensitive.

• – Output can change multiple times during a clock cycle.

• – Output changes while clock is active.

Flip-Flop

• – Clock input is edge sensitive.

• – Output can change only once during a clock cycle.

• – Output changes on clock transition.

Dr. AMMAR ABDUL-HAMED KHADER

22

Sequential Circuit

Dr. AMMAR ABDUL-HAMED KHADER

23

• Introduction to Counter

Asynchronous Counter

• Asynchronous Up/Down Counter

Synchronous Counter

• Synchronous Counter Up/Down

Sequential Circuit: Counter

Introduction

• Counter is a circuit which cycle through state sequence

• Two types of counter

– Asynchronous counter (e.g. ripple)

– Synchronous counter (e.g. parallel)

• Ripple counter let some flip-flop output, to be used as clock

signal source for other flip-flop

• Synchronous counter use the same clock signal for all flip-flop

Dr. AMMAR ABDUL-HAMED KHADER

24

Sequential Circuit: Counter

Asynchronous Counter (Ripple)

• Asynchronous Counter : flip-flop doesn’t change condition

simultaneously because it doesn’t use single clock signal

• Also known as ripple counter because clock signal input as

ripple through counter.

• Modulus (MOD) – the number of states it counts in a complete

cycle before it goes back to the initial state.

• Thus, the number of flip-flops used depends on the MOD of

the counter (ie; MOD-4 use 2 FF (2-bit), MOD-8 use 3 FF (3-

bit), etc.

Dr. AMMAR ABDUL-HAMED KHADER

25

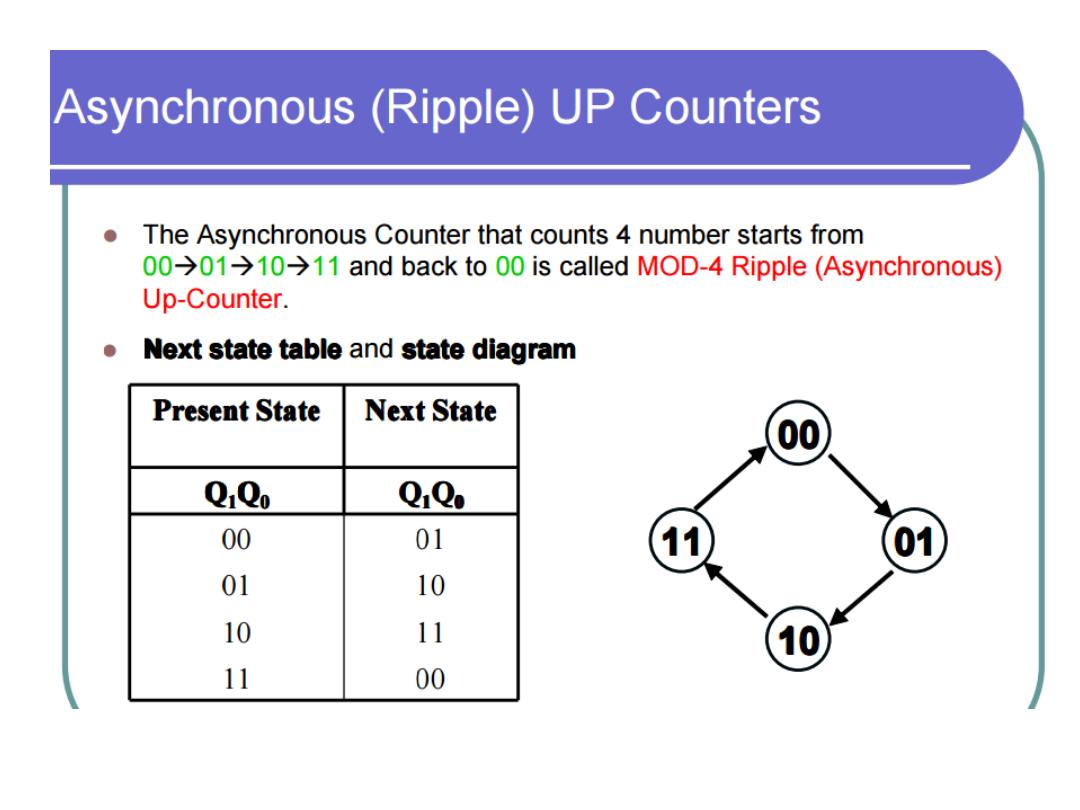

Dr. AMMAR ABDUL-HAMED KHADER

26

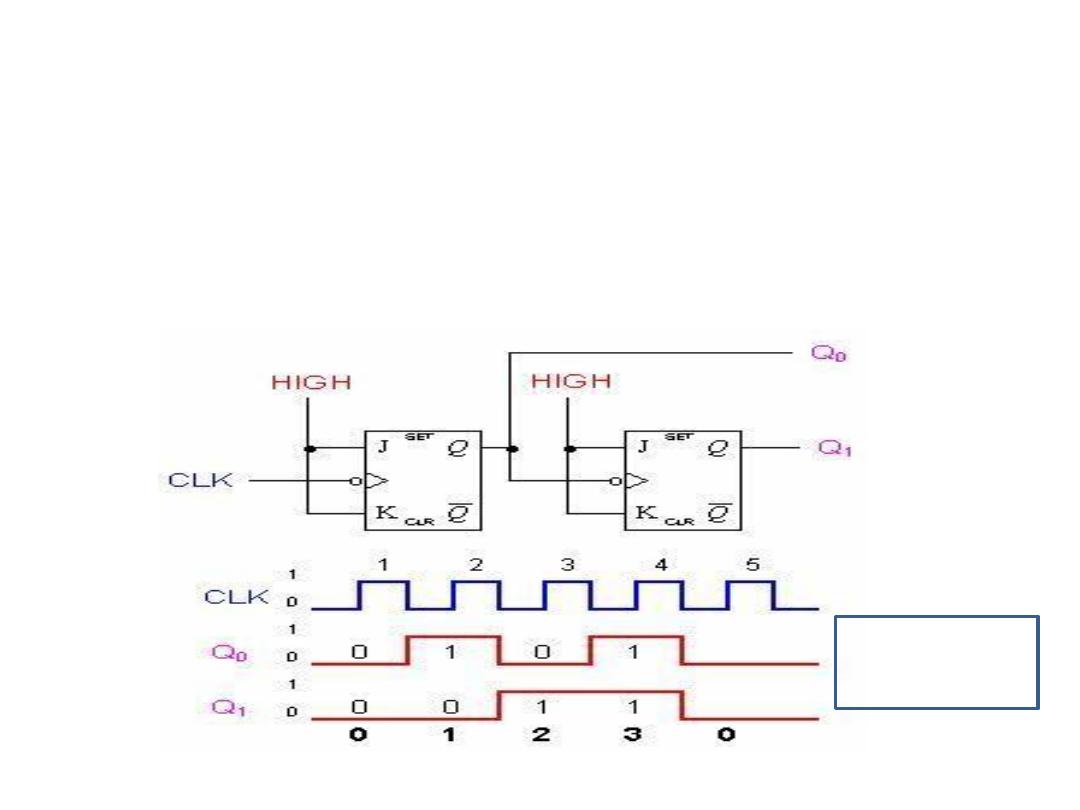

Asynchronous Counter (Ripple)

MOD-4

• Example: 2-bit ripple counter (UP COUNTER)

• Output from one flip-flop is connected to clock input for the

next flip-flop.

Dr. AMMAR ABDUL-HAMED KHADER

27

Timing diagram

00 01 10 11

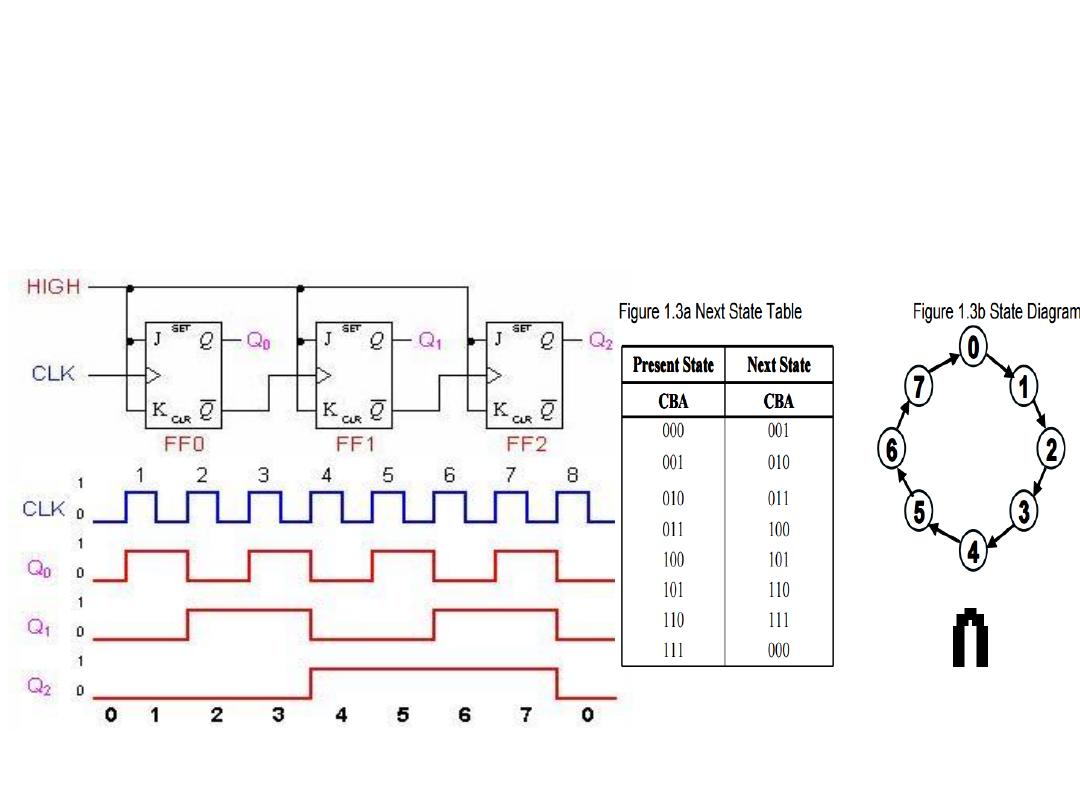

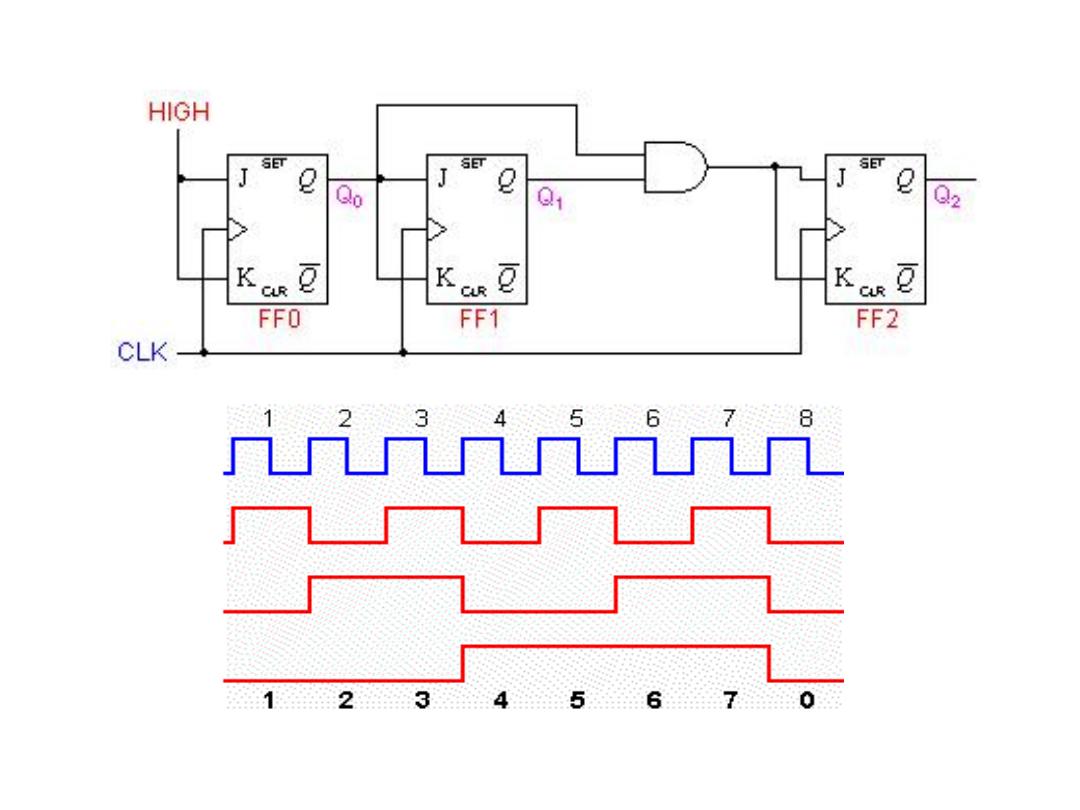

Asynchronous Counter (Ripple)

MOD-8

• Example: 3-bit ripple counter (UP COUNTER)

Dr. AMMAR ABDUL-HAMED KHADER

28

Dr. AMMAR ABDUL-HAMED KHADER

29

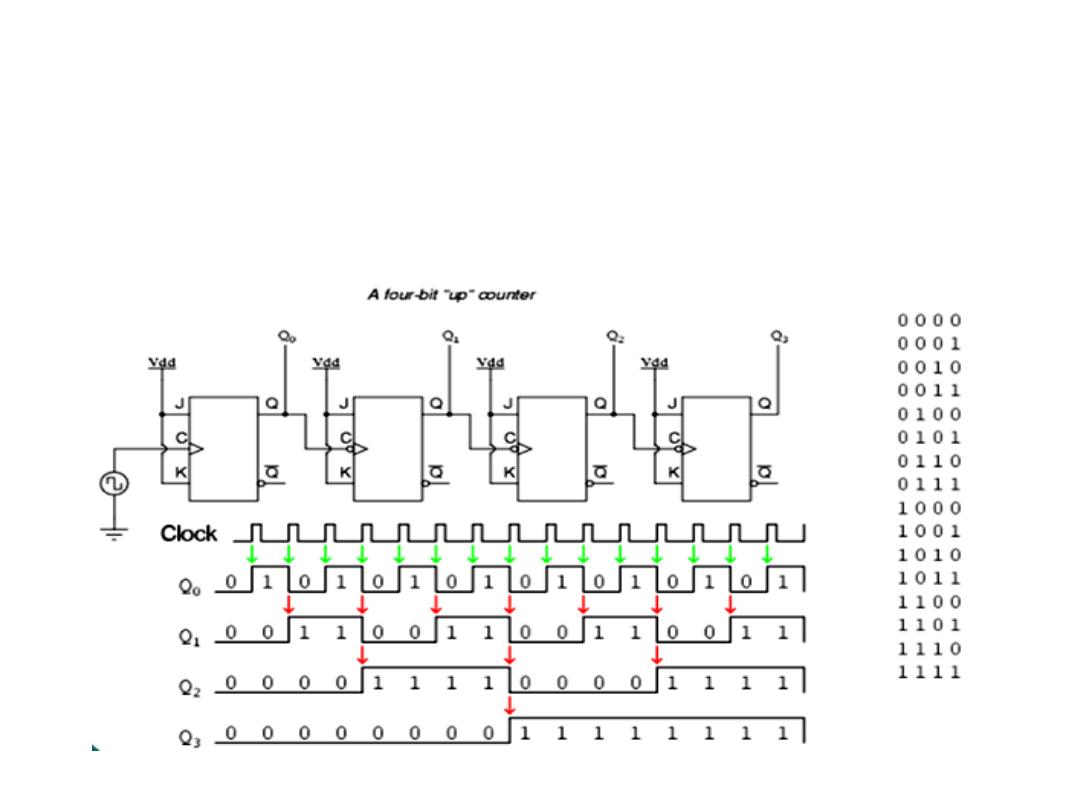

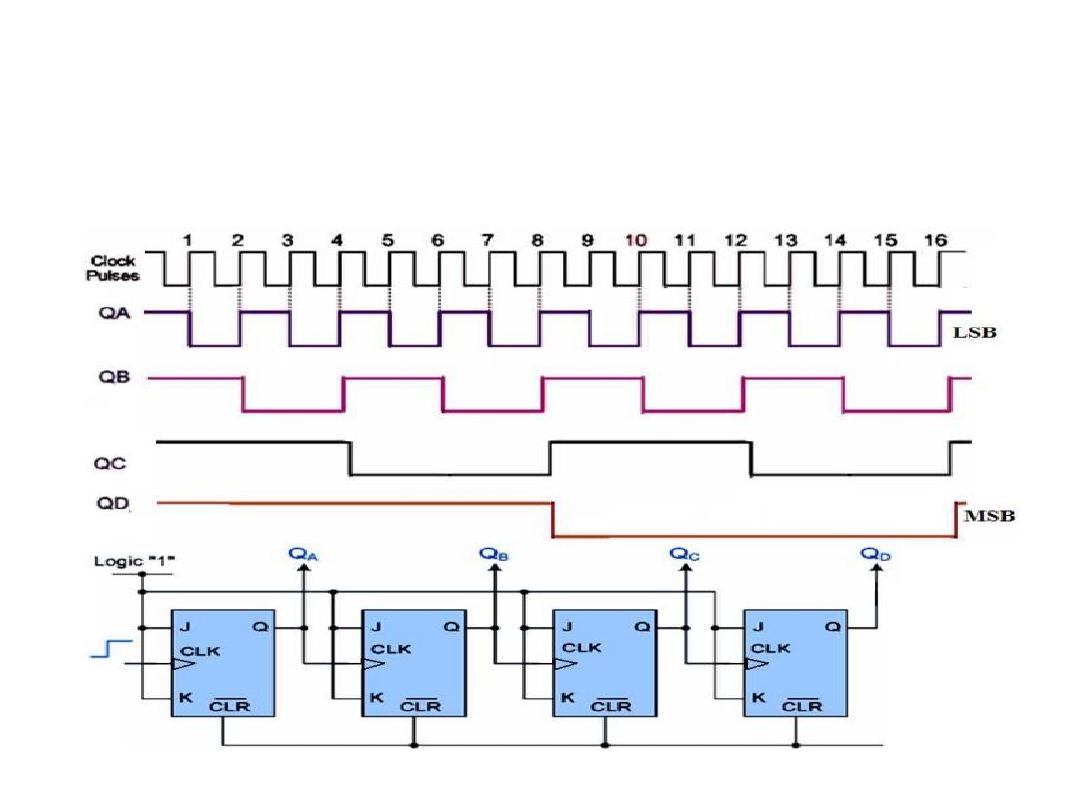

Asynchronous Ripple Counter ((UP COUNTER))

• Example: 4-bit ripple counter (negative edge triggered)

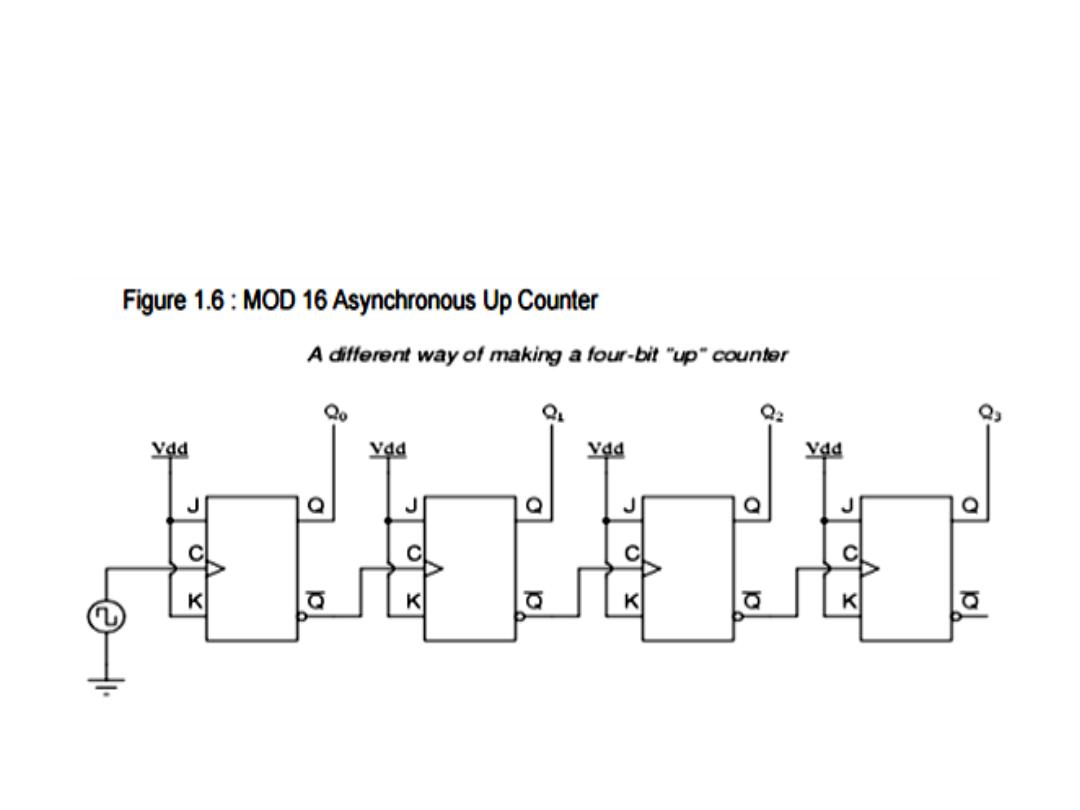

Asynchronous Counter (Ripple)

MOD-16

• (Positive edge triggered)

Dr. AMMAR ABDUL-HAMED KHADER

30

Asynchronous Counter (Ripple)

MOD-16

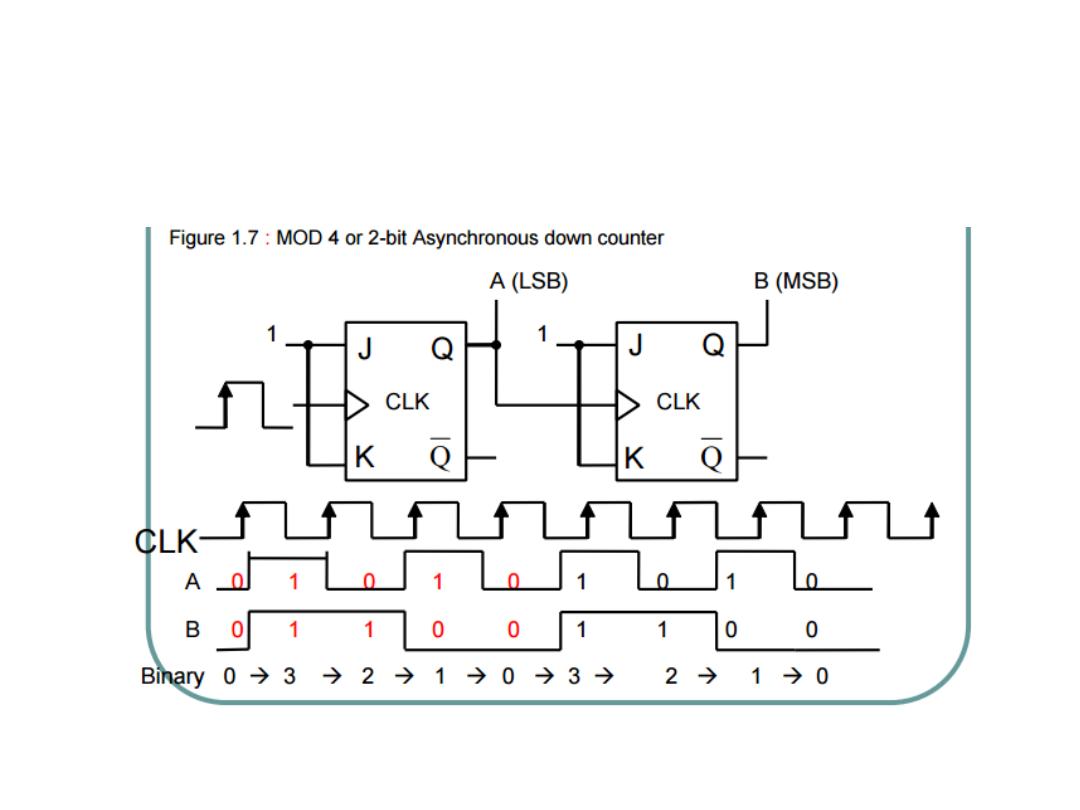

Asynchronous Down Counter

Binary Ripple down counter

• For positive edge triggered flip-flops the counter count down:

• e.g start from15 to 14 to 13 to…….

• The diagram is same as the count up binary counter except that

the flip-flop trigger on the positive edge of the clock.

• If negative edge triggered flip-flops are used then the CLK

input of each flip-flop must be connected to the complement

output of the previous flip-flop. So, when the true output goes

from 0 to 1, the complement will go from 1 to o and

complement the next flip flop as required

Dr. AMMAR ABDUL-HAMED KHADER

31

Asynchronous Down Counter

• 2-Bit Binary Down Counter

Dr. AMMAR ABDUL-HAMED KHADER

32

Asynchronous Down Counter

• 4- Bit Binary Down Counter

Dr. AMMAR ABDUL-HAMED KHADER

33

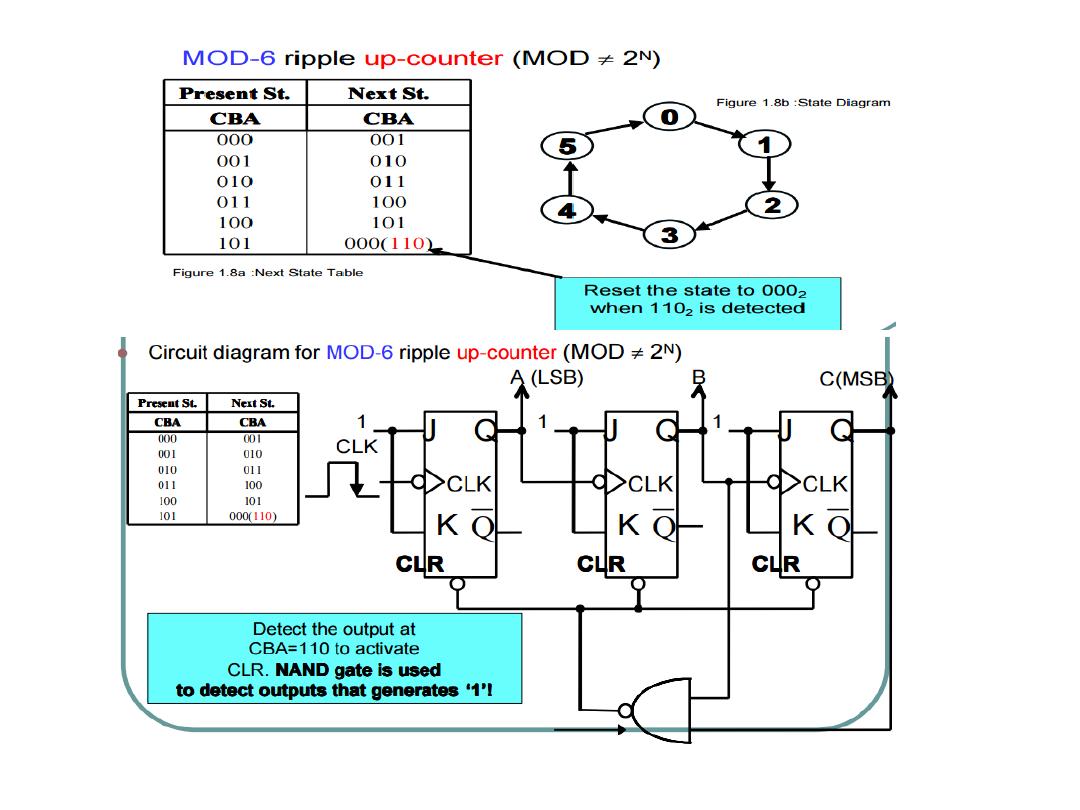

Asynchronous Counter MOD NOT 2

Dr. AMMAR ABDUL-HAMED KHADER

34

Dr. AMMAR ABDUL-HAMED KHADER

35

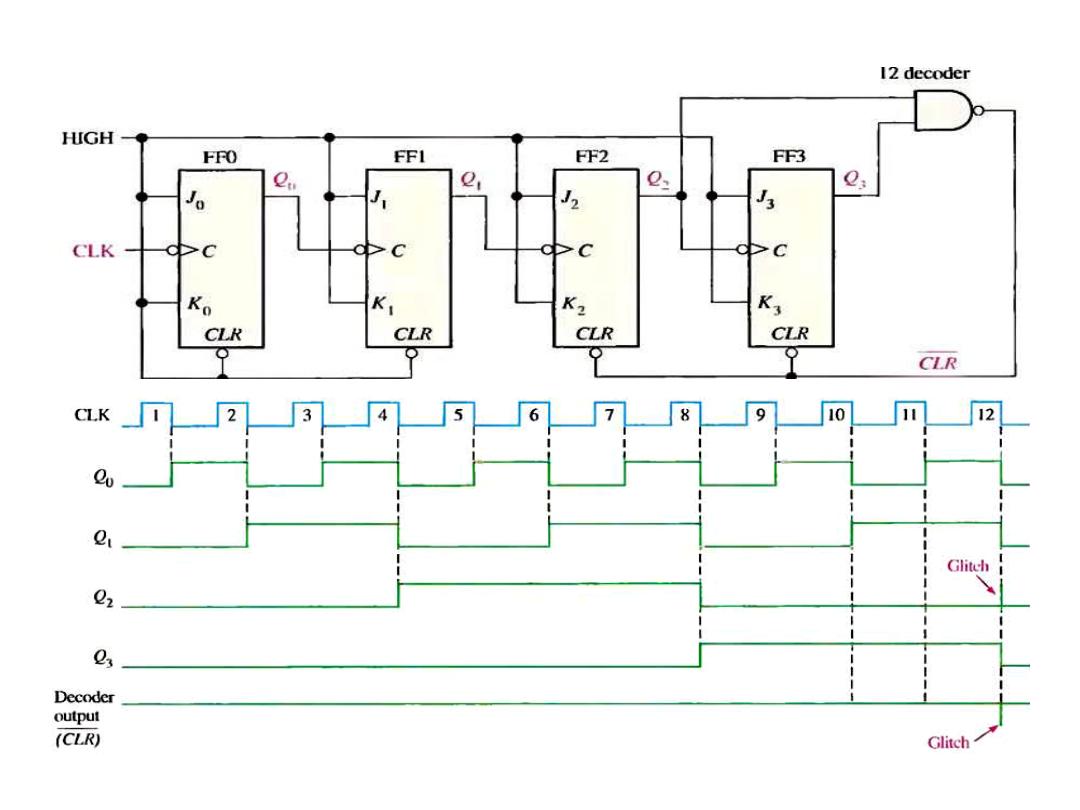

• Example: Show how an asynchronous counter can be

implemented having a modulus of twelve with a straight

binary sequence from 0000 to 1011.

• Solution: Four FF are required. When the counter gets to

its last state 1011, it must recycle back to 0000 rather than

going to its normal next state (1100)

Dr. AMMAR ABDUL-HAMED KHADER

36

Dr. AMMAR ABDUL-HAMED KHADER

37

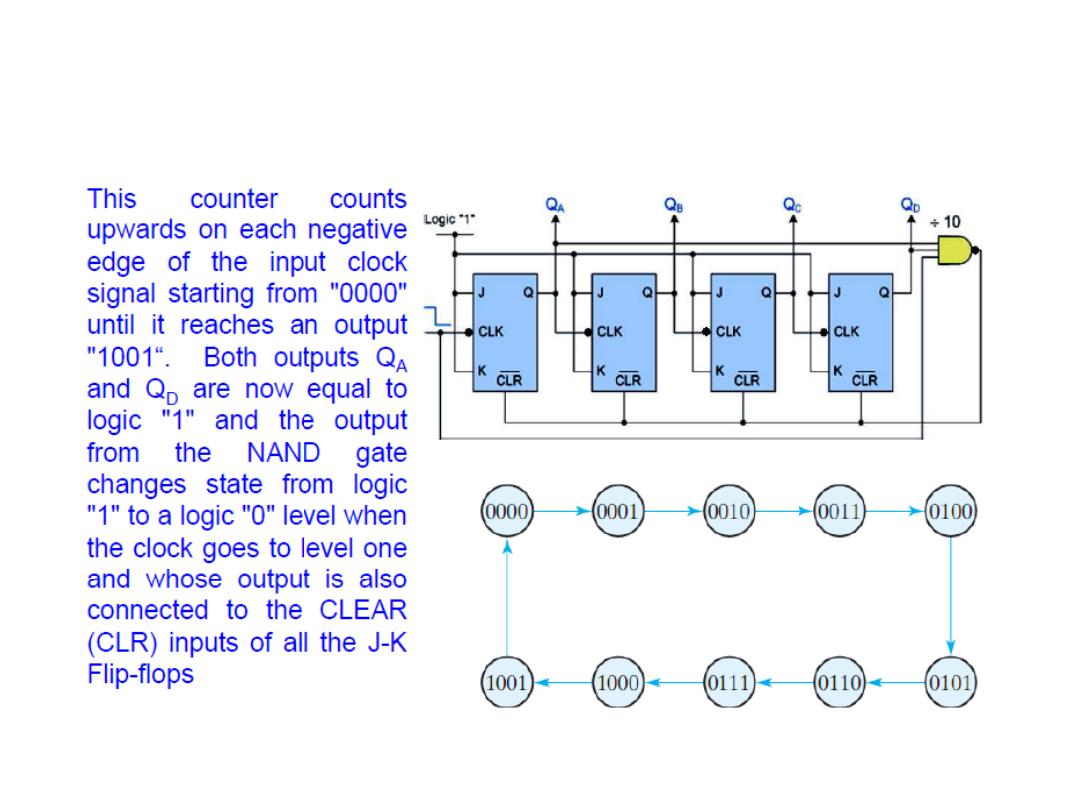

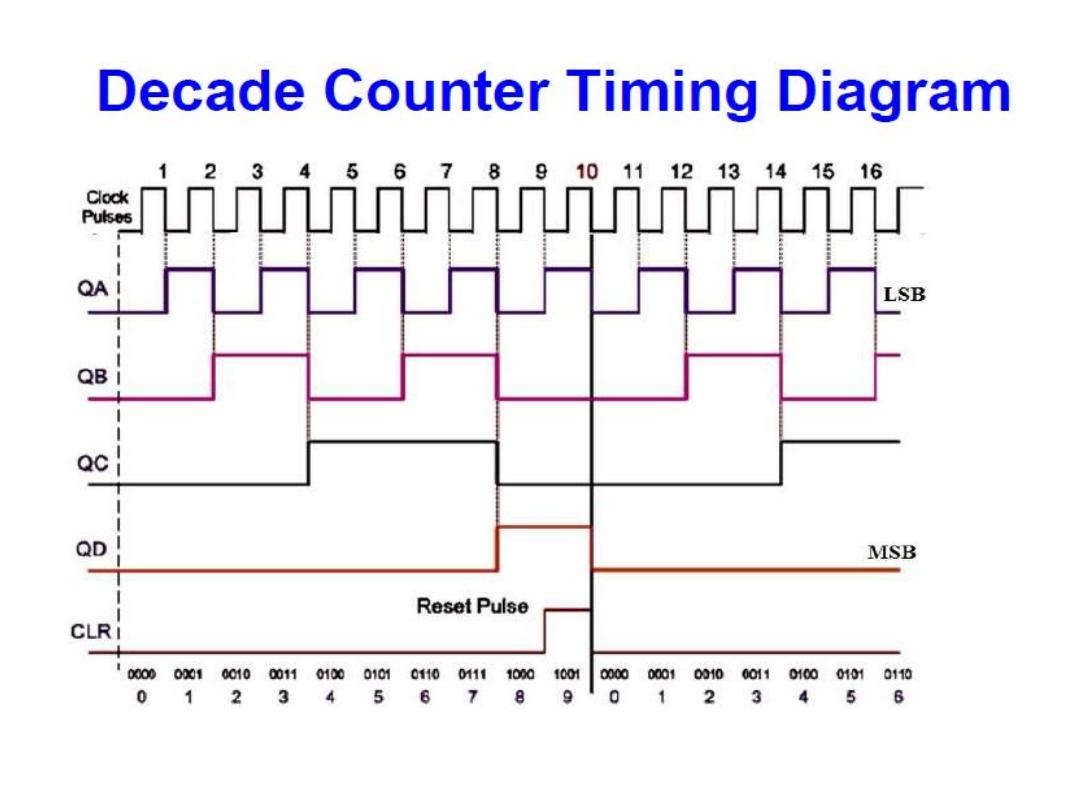

BCD Ripple Counter, Decade Counter

Dr. AMMAR ABDUL-HAMED KHADER

38

Dr. AMMAR ABDUL-HAMED KHADER

39

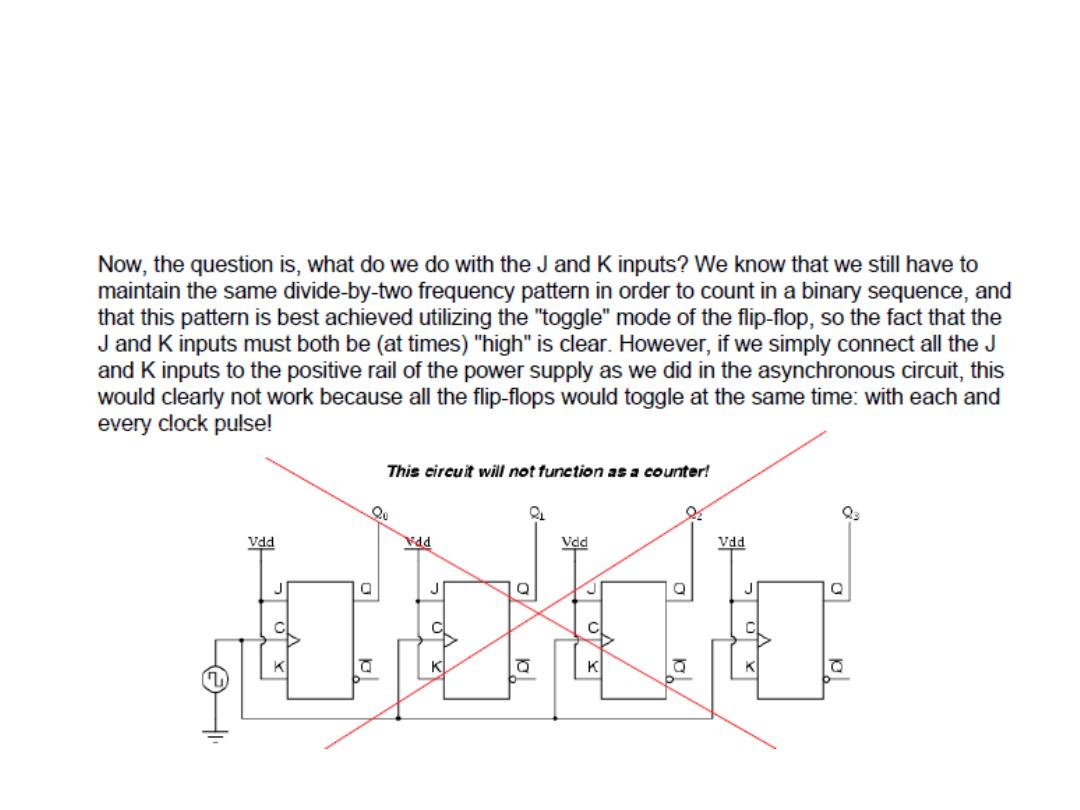

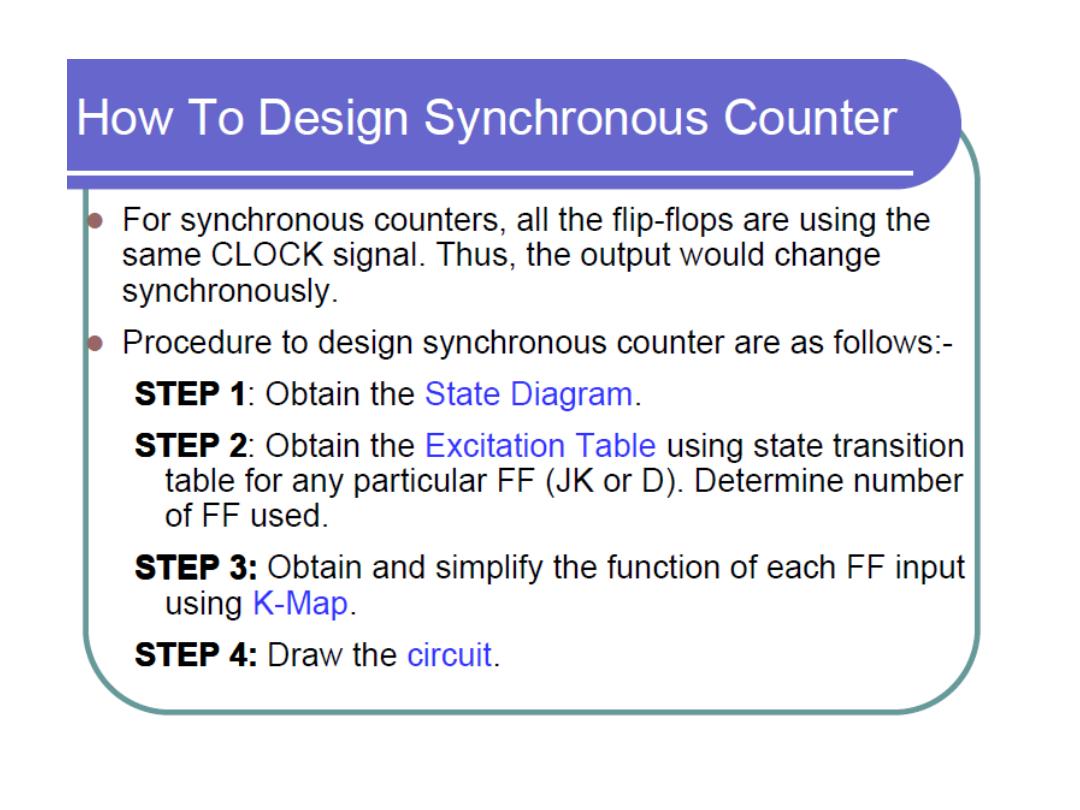

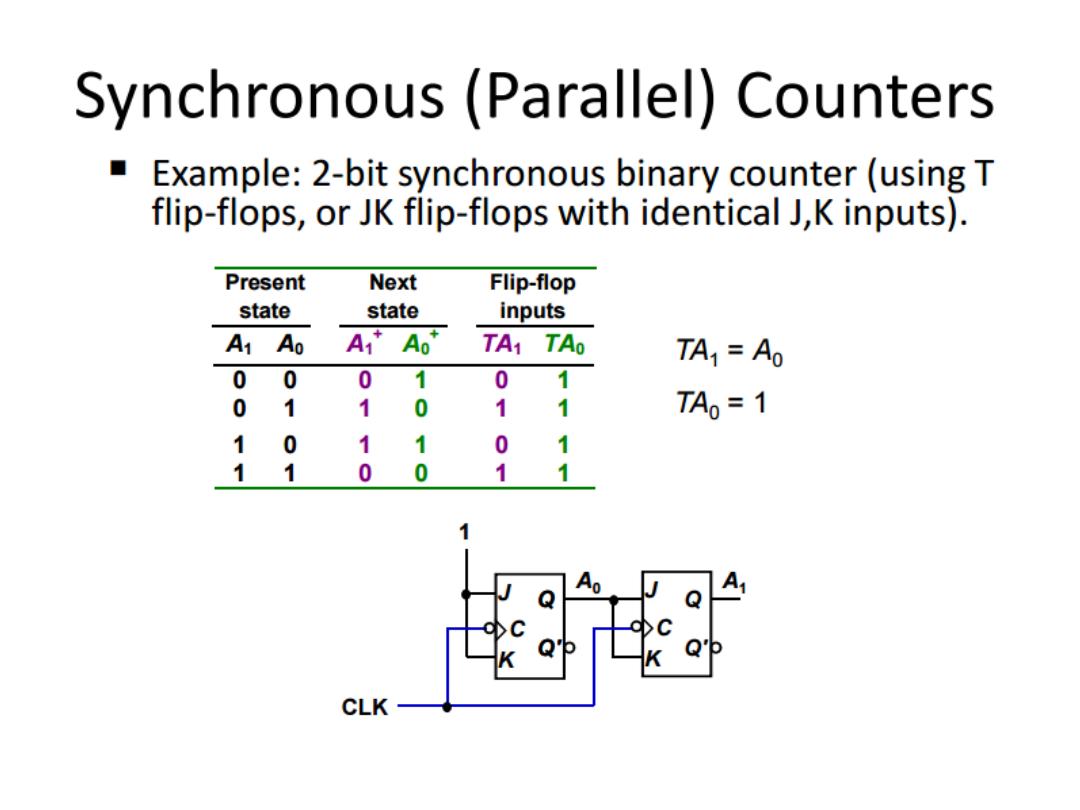

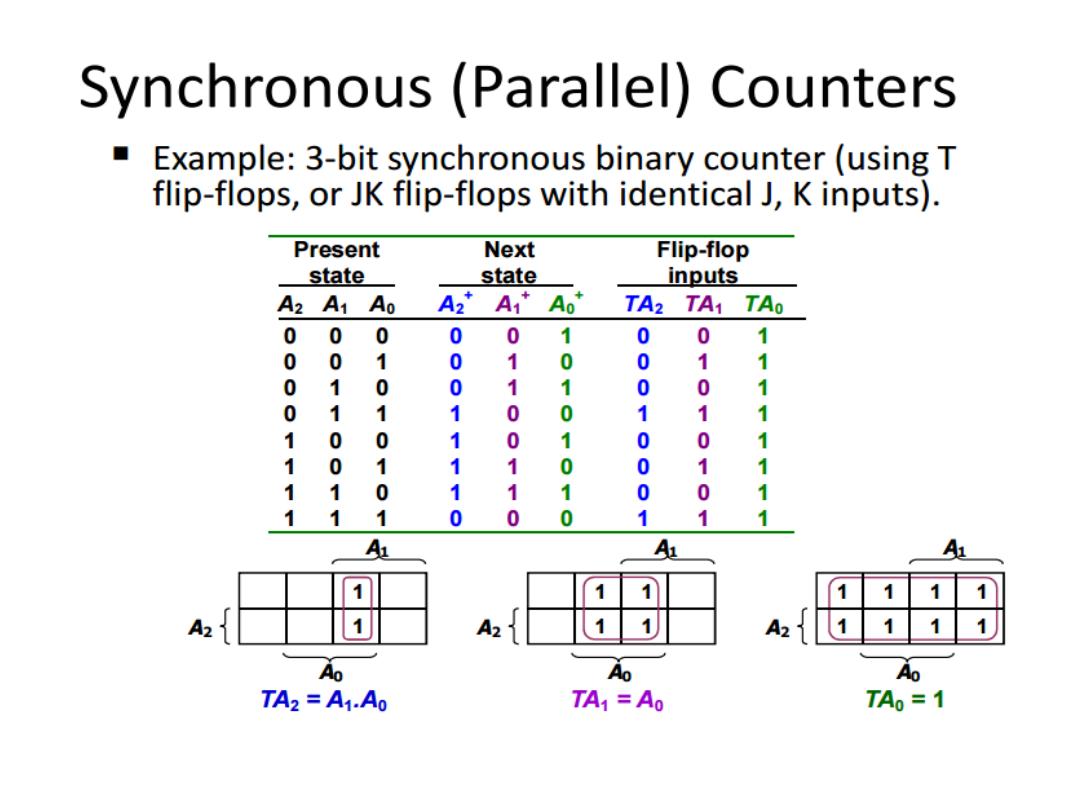

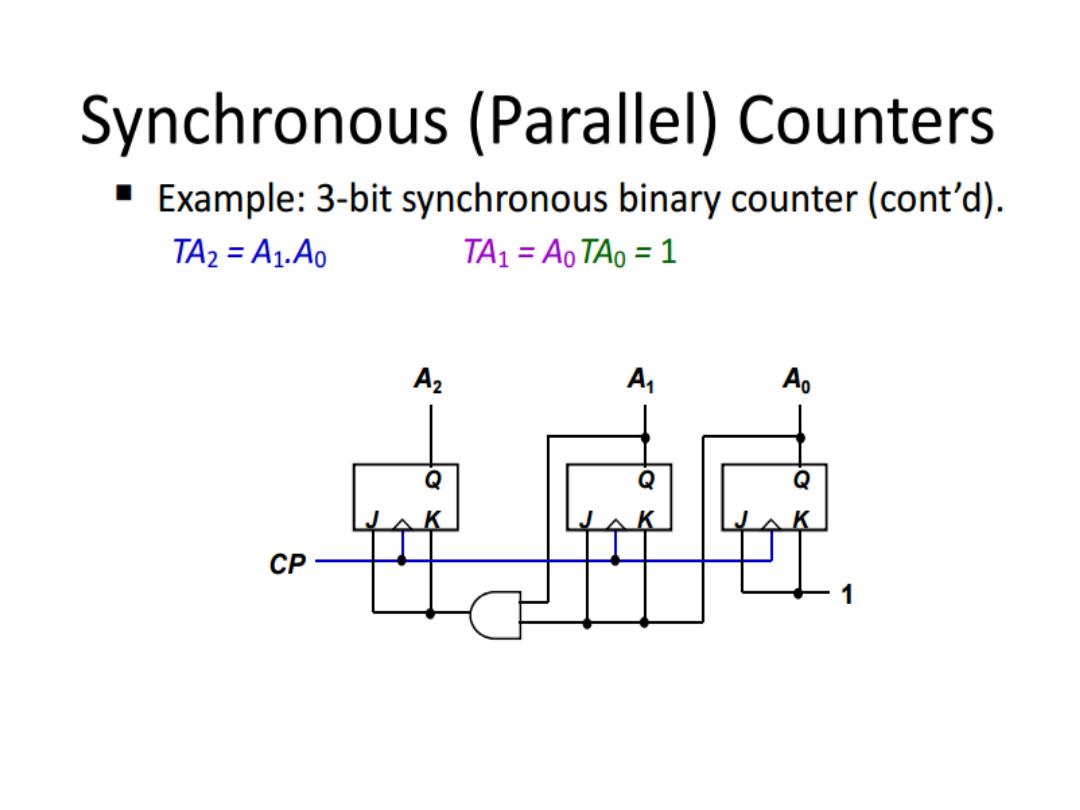

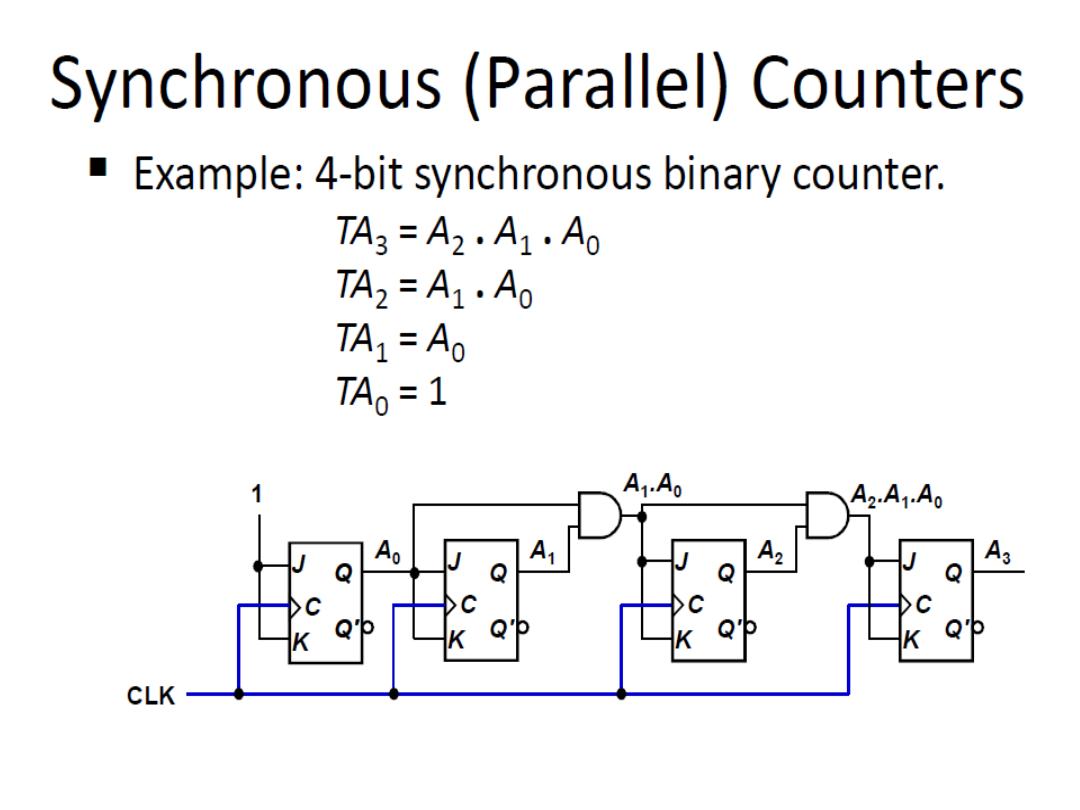

Synchronous Counters (Parallel)

• FFs in the counter are clocked at the same time by a common clock

pulse.

Dr. AMMAR ABDUL-HAMED KHADER

40

Dr. AMMAR ABDUL-HAMED KHADER

41

Dr. AMMAR ABDUL-HAMED KHADER

42

Dr. AMMAR ABDUL-HAMED KHADER

43

Dr. AMMAR ABDUL-HAMED KHADER

44

Dr. AMMAR ABDUL-HAMED KHADER

45

Dr. AMMAR ABDUL-HAMED KHADER

46